SRAM乒乓操作

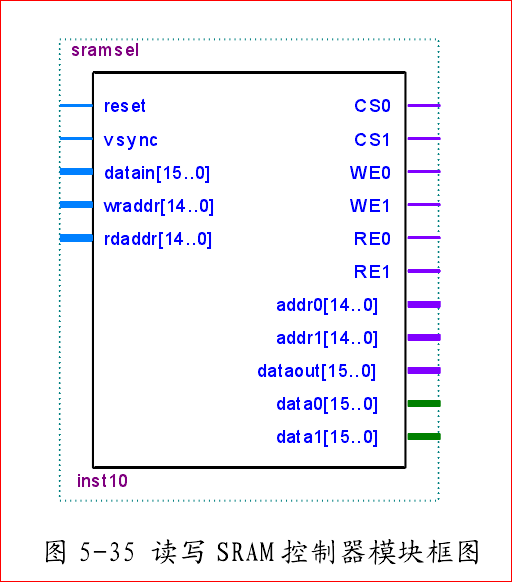

视频操作的有个模块。想实现两片SRAM乒乓操作,

我有两个疑惑?

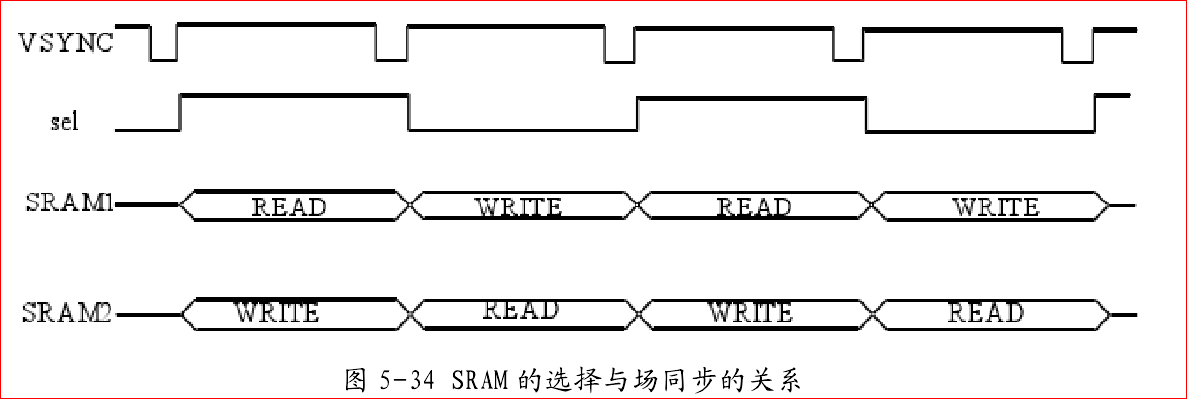

1.图一中VSYNC信号(场同步信号)是否可以直接用作时钟信号,是否还需要另加一个时钟信号clk? 因为有读时钟rdclk和写时钟wrclk。如果需要加时钟,那么应该设置这个时钟为多少?或是根据什么设置?(我个人觉得不能直接用VSYNC作为一个时钟信号,因为我用示波器测过这个信号,不像时钟信号那么稳定。)

2.图2中通过VSYNC产生一个选择信号,通过信号SEL判断操作SRAM1和SRAM2,那么第一阶段(只是写SRAM1,而没有读SRAM2)该怎么判断?

PS:本人新手,弄了好久了,感觉都不对,希望大家能多给指点。谢谢!

这不是和fifo差不多么

进行一个判断

进行一个判断是什么意思?能说的具体点吗

是差不多的

VSYNC不能作为时钟,最多作为时钟使能,时钟设置大小以采用VSYNC低脉冲大小为宜,因为很明显你的sel使能是与VSYNC相与共同作用的,为了保证读写持续一拍,那么时钟设置就是VSYNC的低脉冲宽度,或者说先产生系统时钟,其它以此为基准,如VSYNC.关于读写,未写先读问题,稍微加点控制就能避开了

恩,谢谢你,那个SEL信号并不是输入信号,是根据VSYNC的上升沿产生的翻转信号,然后根据SEL信号再判断读写sram0/1情况, 其实有系统时钟,有单独的时钟模块,读写时钟都是根据系统时钟产生的,在这个模块中不知道用到哪个时钟?还是需要再产生一个新的时钟,那么新的时钟应该设置为多少?

对于那个未写先读的问题,我没有想到怎么控制,因为输入端口的控制信号其实只有一个场同步信号(VSYNC),

刚学习没多久,这是我尝试编写的第一个程序,还有很多不懂得问题,希望可以多多指点,如果您感兴趣,我可以把代码发给你,你抽时间帮我看看。谢谢!

为什么还要产生新的时钟?你的场同步信号的源时钟是什么?时钟同源才是同步设计啊

其实你的目的很明确,就是RAM乒乓操作,自己设计也能完成.你这个RAM乒乓类似模拟双端口RAM的功能,因为我看是交替读写,奇偶地址分开的,读写使能也能看出.

恩,受教了,谢谢你,因为这个在别人的论文中看的,就想按照这个思路来写,VSYNC信号是有个65M的源时钟,这个模块实现的功能就是乒乓操作控制外部SRAM存储一帧图像。想问下为什么我设置的简单双端口RAM,有时候会输出数据,有时候输出的一直为高阻态,仿真时提示的错误:Block Memory Generator CORE Generator module system_top_tb.uut.data_cut1.ip_ram1.inst.\native_mem_module.blk_mem_gen_v7_2_inst is using a behavioral model for simulation which will not precisely model memory collision behavior.

这个可能是仿真工具提示的warning,是不是高阻,你看看读写使能是否正确,正常的RAM端口一般就是

.sys_clk

.ram_cs

.ram_wen

.ram_ren

.ram_addr

.ram_in

.ram_out

这些,输出是高阻看看相应地址的输入是什么?当前读写使能又是什么?

您做的怎样了,最近也在看关于乒乓操作的内容

LED显示屏。类似于LED大屏,我也是刚做,可以一块探讨,

在上电以后初始化2片SRAM,所有地址跑遍,之后再进行乒乓操作。如果是同步时钟乒乓,可以都用存图像的写时钟,如果是异步时钟乒乓,需要考虑时序分析,建议用状态机等待。

谢谢你,会按着你说的方法试试看。