求助一个verilog语法问题

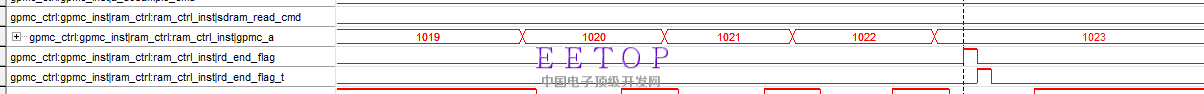

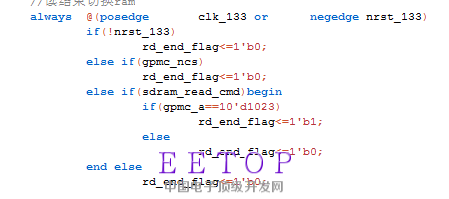

向大家求教一个问题,我有一段代码是这样写的,我认为sdram_read_cmd为低的时候,rd_end_flag是不可能拉高的,但在signaltap中出现了拉高的情况,想请教大家这是什么问题,是不是这种写法不是我想象的那样,还是有其他东西我不知道的,求大神指教,该如何修改

向大家求教一个问题,我有一段代码是这样写的,我认为sdram_read_cmd为低的时候,rd_end_flag是不可能拉高的,但在signaltap中出现了拉高的情况,想请教大家这是什么问题,是不是这种写法不是我想象的那样,还是有其他东西我不知道的,求大神指教,该如何修改

sdram_read_cmd信号波形是不是代码module里的sdram_read_cmd信号?rd_end_flag有没有可能在别处有赋值?

rd_end_flag为高的条件是:(gpmc_ncs==1‘b0) && (sdram_read_cmd==1’b1) && (gpmc_a==10'd1023);

假设图中: 最上面是gpmc_ncs,最下面是sdram_read_cmd. 脉冲之前正好满足了这个条件,因为时钟赋值输出延迟了。所以signaltap图是正确的。

没看出问题,我觉得这样写是没问题的。也许你该另外写个always专门监视sdram_read_cmd,不正常的时候弄个什么指示之类的。还有,你也要考虑别的方面的原因,比如烧错了bit文件之类的

额,我这个图很清楚吧!为何你会认为最上面是ncs,最下面是cmd?好奇怪

问题已解决,将整个工程fmax拉高即可解决

没看懂你说的意思,Fmax拉高和信号的赋值有啥关系

也就是说这可能和时序不稳定有关系

路过,看看

路过 看看

都是同一时钟域的信号吗?

跨时钟域使用信号的话,必须先同步啊。

和这个无关,在刚出现这问题的时候就已经考虑过跨时钟域的影响了,但最终解决方法说明不是这个问题。

提高FMAX,是在clk的约束方面吗?

以前按正常约束有这个问题,提高Fmax约束后,问题消失了。

这个解决问题的方法让我很不能理解。

如果说时钟正确的约束了,而且没有时序告警,又没有潜在的跨时钟域的问题。

那这个问题应该是芯片的问题啊,起码芯片的performance和时序仿真模型不符啊。

建议小编不要放过这个问题,要不然大批量的时候,肯定还会有问题。

代码写得不好

fmax和约束时钟没有什么关系!约束时钟只是告诉软件我这个系统跑多快!fmax和整体代码有关系,就像楼下说的,代码写的不好,在各种计数器后加寄存器,减少延时,就可以提高fmax,最终解决是我公司一个老司机叫我尝试一下,然后我根据时序分析的结果,在时间余量比较差的计数器后加了寄存器,问题就解决了,当然像你说的,以后可能还有问题,但现在至少概率很低了,signal tap的波形图和代码你也看到了,根据代码绝对不可能出现这种问题的,所以提高整体代码的时序也许就是唯一的解决办法。

时序约束怎么可能跟fmax没关系。所以你之前都没做时序约束 不看综合报告吗......

代码风格再差,只要没有语法错误,又没有时序问题(这里包括跨时钟域)。 FPGA也应该按照代码描述,实现代码功能。

把你的SDC文件和timing report拿出来,大家分析一下,相信一定能够找到最根本的原因的。

不过,顺便膜拜老司机。

学习了,高手啊

出现了恶稳态的情况?

时序不对的话,对signaltap的图是不可信的。