奇数分频

时间:10-02

整理:3721RD

点击:

请教各位兄弟,现在一个ASIC项目中需要一个5分频,将30MHz时钟分频成6MHz输出,看了百度上的一些资料,基本上都是用相或的方法实现的,且同时用了时钟的上下沿,但老大明确说不允许同时用时钟的上下沿,请问各位有什么好方法?

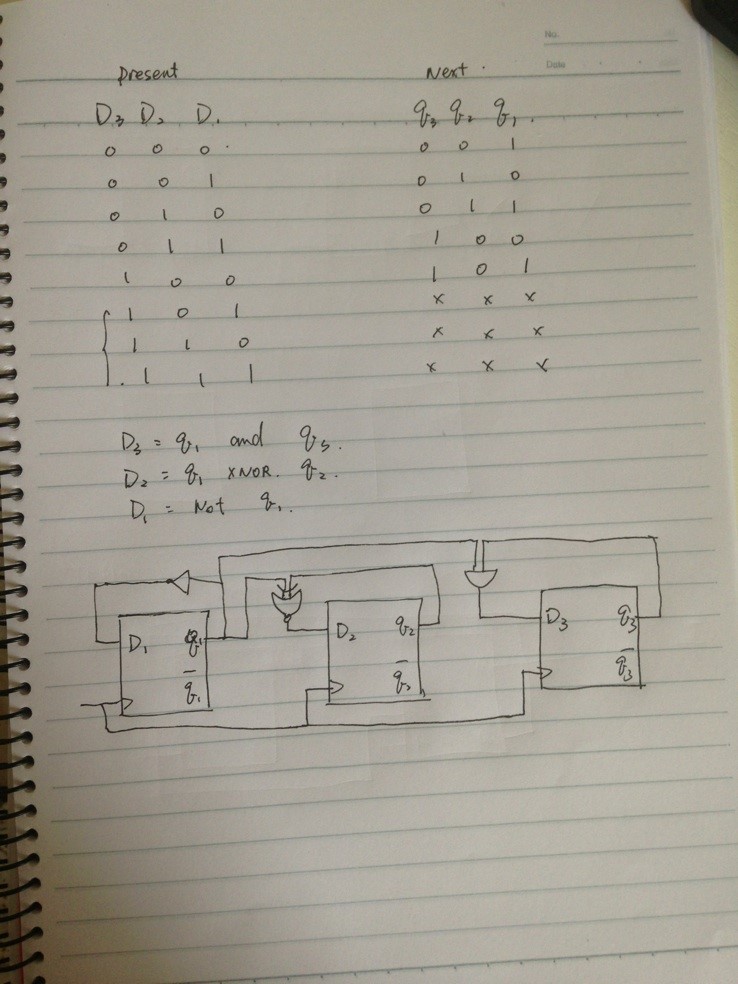

自己看吧,解都在图上

如果占空比没有要求,使用上升沿时钟就可以了;如果要求占空比50%,只能同时使用正反相位时钟。你老大的要求是指不能出现negedge clk的写法吧,那你使用posedge clk_n咯。

自己看吧,解都在图上

一般来讲,双沿触发在设计中是不被允许的,某些综合工具也不支持;照目前你设计而言,30Mhz属于中低频设计了,一般而言是用其上升沿触发,除非对占空比有特定要求必须为50%,通常用posedge触发分频得到占空比为2:5或3:5的6Mhz时钟即可。

谢谢,问了老大,与你的见解一样,可以这么做

高速设计中,一般都是有独立的x分频clk,并且相关clk一定是balance的。目的是保证clk align.

非高速设计中,不一定独立create一个root clk, 可以用比如ck_latch产生duty cycle不是50%的clk,和clk-gating很类似,只不过在最后的CTS做balance即可。