对FALSE PATH的理解

对FALSE PATH的理解

最近做了一点FPGA方面的工作,在用QuartusII对代码进行综合时四处查找资料,总算是对FALSE PATH有了一点点的理解,总得来说,FALSE PATH就是我们在进行综合分析时,不希望综合工具进行分析的那些路径。写出来和大家一起讨论。

在QuartusII的一个培训文档里面解释了什么时候要用到FALSE PATH:

1. 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。

2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

下面举例说明:

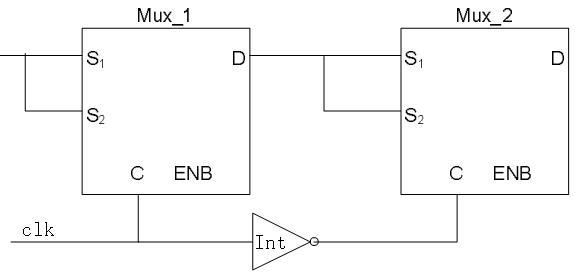

先看图1,MUX_1和MUX_2是两个多路选择器,MUX_1的使能端C接到时钟clk,MUX_2的使能端C接到clk的反。于是可以发现MUX_1的S1端口是不可能经过MUX_2的S1端口到达MUX_2的D端口的,同理MUX_1的S2端口是不可能经过MUX_2的S2端口到达MUX_2的D端口。于是我们就不希望综合工具对这两条路径进行分析,就是说这两条路径就是我们所说的FALSE PATH:

set_false_paths –through Mux_1/S1 –through Mux_2/S1

set_false_paths –through Mux_2/S2 –through Mux_2/S2

图1

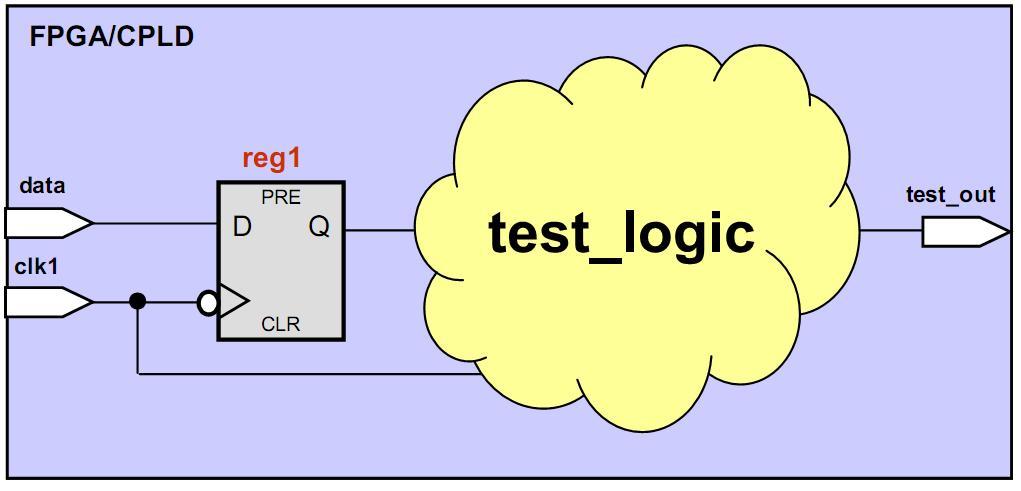

再看图2,模块test_logic表示一个测试逻辑,它并不真正实现我们电路的功能,只是为了测试电路功能。所以我们就不希望综合工具对这这些路径进行分析,就是说这些路径就是我们所说的FALSE PATH:

图2

set_false_path –fall_from clk1–to [get_pins test_logic|*|datain]

set_false_path –from [get_pins test_logic|*|clk] \

-to [get_pins test_logic|*|datain]

set_false_path –from [get_pins test_logic|*|clk] -to [get_ports test_out]

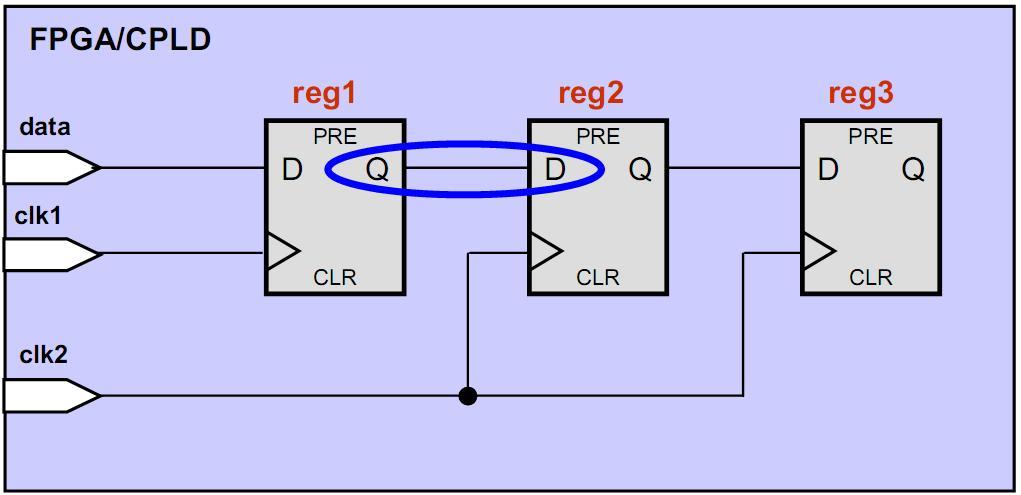

然后看图3,reg1的输出和reg2的输入跨越了不同的时钟域clk1和clk2,我们不希望综合工具对这这些路径进行分析,就是说这些路径就是我们所说的FALSE PATH:

set_false_path –from [get_pins reg1|clk]–to [get_pins reg2|datain]

图3

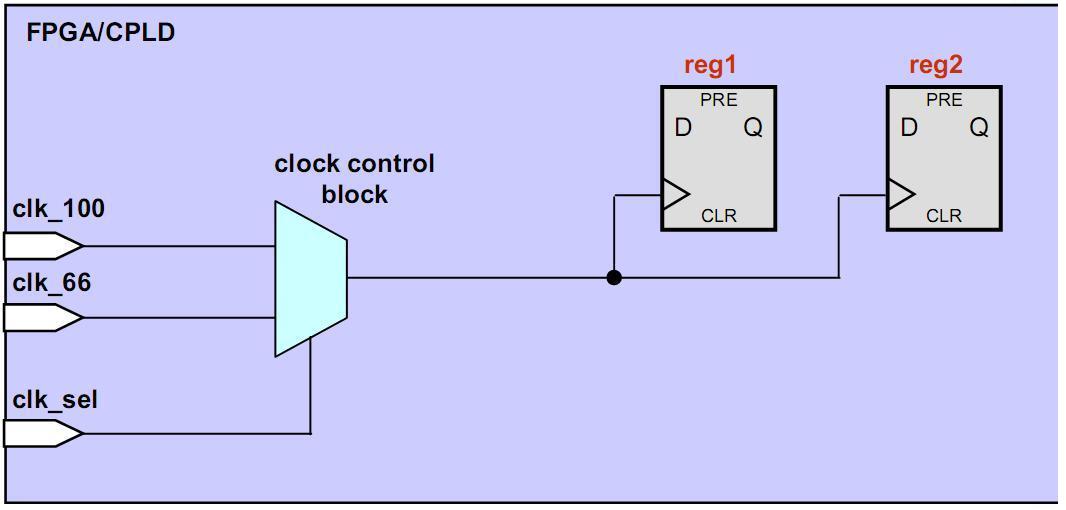

最后我们看图4,clk_100和clk_66仍然是两个不同的时钟域,这也是FALSE PATH:

set_false_paths –from [get_clocks clk_100] –to [get_clocks clk_66]

set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]

实际上,这两条FALSE PATH可以用一条命令来代替:

set_clock_groups –exclusive –group {clk_100} \

–group {clk_66} –group {clk_200}

这就涉及到set_clock_groups 命令了,我们以后再说。

图4

接触数字电路的时间不长,当然对数字电路的理解就不深刻。这次就把我对FALSE PATH的理解写出来,希望得到大家的指点。

不胜感激,多谢!

附件:

都是copy来的资料,false path说到底就是时序分析时不需要分析的路径。

呵呵 谢谢~

其实简单的说就是让工具不优化这条路径上的时序

LZ讲的不错。

基本上就是小编讲的那样

关注中 !111

顶小编。

他们说我在灌水,你怎么理解?

1# wjx197733

回答。我貌似确实在灌水。还请原谅。

一小子传个东西。分了好几十份。一份也就3M吧。把大家的钱都“抢”了

11# heimareed

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

好好

哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦哦噢噢噢噢

平平平平平平平平平批评批评批评批评批评批评批评批评批评

jjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjjj

轻轻轻轻轻轻轻轻轻轻轻轻巧巧轻轻轻轻轻轻轻轻轻轻轻轻巧巧轻轻轻轻轻轻轻轻轻轻轻轻巧巧亲切慰问慰问慰问我

好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好

mmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmmm

不错,不错。

学习了

多谢 好东西啊 一定要收藏啊!

感激用心解說!

感觉很多都讲得不对。比如例子1,不是上升沿和下降沿之间的路径就一定可以设置false path。

说的好!

学习了

正在学习,加油啊