用modelsim做门级仿真时,怎么观察中间信号的变化

时间:10-02

整理:3721RD

点击:

求大神解决。我需要对一个系统进行功能仿真和门级仿真。这个系统的RTL视图如下所示:

[attach]671505[/attach]

需要观察handshack1内部的寄存器,名字叫state。

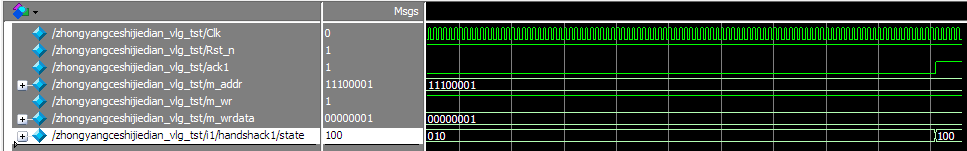

在进行功能仿真的时候,可以在object中找到这个信号,如下图:

[attach]671504[/attach]

[attach]671504[/attach]

但是在门级仿真时,在object中找不到这个信号,如下图:

我看到其他人对于这个问题的回答是:

在testbench里面用层次化调用的方法,可以查看内部的寄存器。如:testbench模块名是simTop,顶层模块名是Top,内部待观察的信号名是data(设8位),那么只要在testbench里面写一句:wire [7:0] testdata=simTop.Top.data即可。

我试了好久这个方法,用modelsim仿真的时候就会出现问题而无法仿真,不知道是因为这个wire是加错地方了,还是调用写错了。要是调用写错了该怎么写呢?

[attach]671505[/attach]

需要观察handshack1内部的寄存器,名字叫state。

在进行功能仿真的时候,可以在object中找到这个信号,如下图:

[attach]671504[/attach]

[attach]671504[/attach]但是在门级仿真时,在object中找不到这个信号,如下图:

我看到其他人对于这个问题的回答是:

在testbench里面用层次化调用的方法,可以查看内部的寄存器。如:testbench模块名是simTop,顶层模块名是Top,内部待观察的信号名是data(设8位),那么只要在testbench里面写一句:wire [7:0] testdata=simTop.Top.data即可。

我试了好久这个方法,用modelsim仿真的时候就会出现问题而无法仿真,不知道是因为这个wire是加错地方了,还是调用写错了。要是调用写错了该怎么写呢?