verilog除法问题

时间:10-02

整理:3721RD

点击:

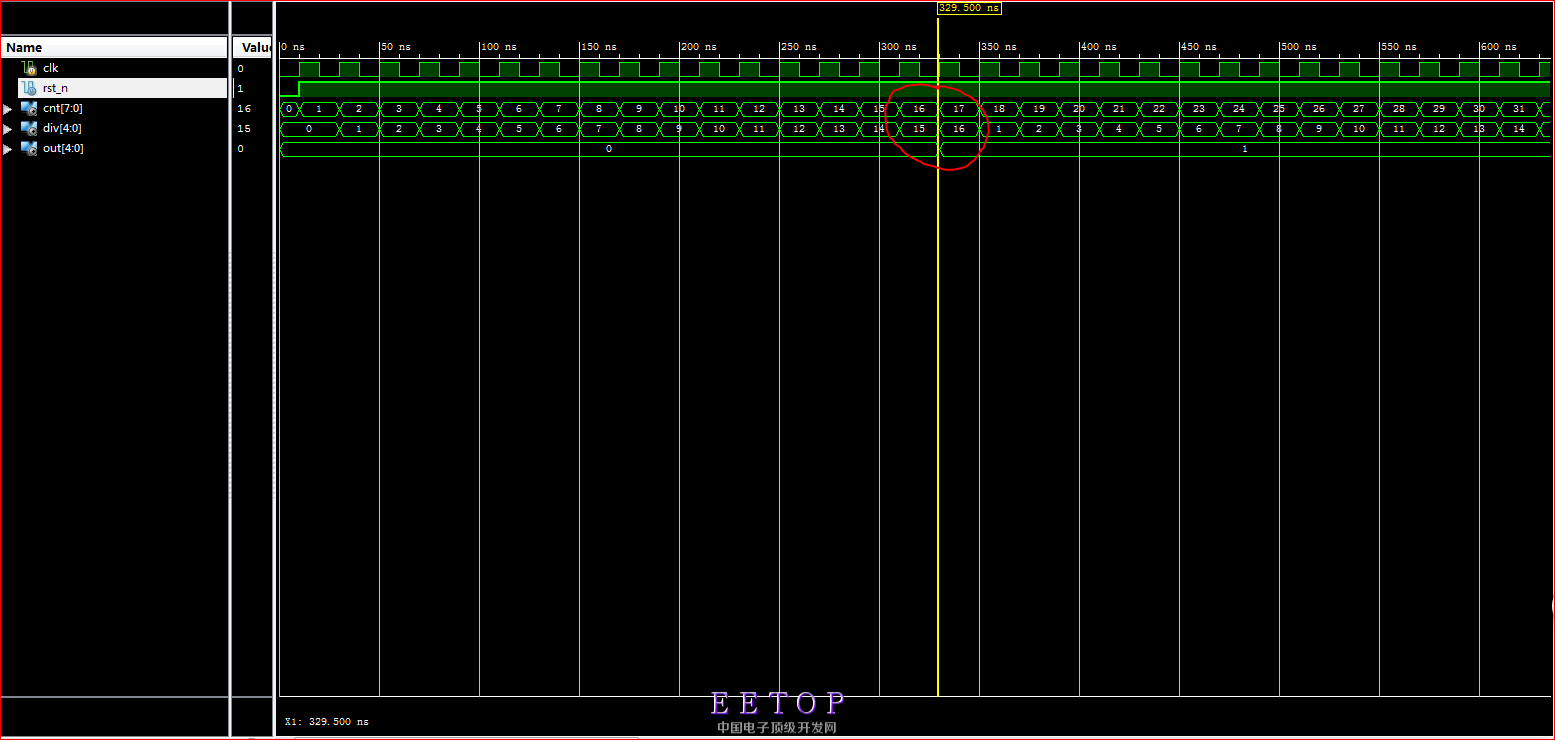

大家好,想知道FPGA到底能不能取模运算,然后我自己编写简单的代码,仿真的时候出现点问题,余数出现延时,想知道怎么处理,谢谢!

- module shift(

- clk,

- rst_n,

- cnt,

- div,

- out

- );

- input clk;

- input rst_n;

- output [4:0] out;

- output [7:0] cnt;

- output [4:0] div;

- //---------------

- reg [7:0] cnt;

- always @ (posedge clk or negedge rst_n) begin

- if(!rst_n) begin

- cnt <= 8'd0;

- end

- else begin

- cnt <= cnt + 1'b1;

- end

- end

- //-------------------

- reg [4:0] out;

- reg [4:0] div;

- always @ (posedge clk or negedge rst_n) begin

- if(!rst_n) begin

- out <= 5'd0;

- div <= 5'd0;

- end

- else begin

- out <= {cnt >> 4};

- div <= (cnt - 16*out);

- end

- end

-

- endmodule

cnt信号右移4位(16),所以cnt需要计数到16才能让out为1

都是在时钟上升沿的时候将右边的表达式计算一下赋值给左边out和div,out的值先被计算出来,之后div的值是跟随out变化而变化。它们不是同步啊,所以当然要有延时。

谢谢你.那么应用到电路中是不是有影响?或者是有什么办法可以改进。

这样的画,你的div就和out没有关系了,应该就不存在延时问题吧

out <= {cnt >> 4};

div <= (cnt - 16*(cnt >> 4));

不会啊,还和原来一样

本来结果就是在下一个时钟啊,16取模16不就是0

你说的对,他的仿真结果是有问题的,改过之后就对了。下一个时钟输出商和余数。