请教一个时序约束的问题

ALTERA 的输入有差分时钟输入:clkp/clkn 频率240MHz

差分数据输入:datap[1:0]/datan[1:0] 480Mbps

数据端口配置成LVDS,双沿采集,数据已经中心对齐了

我的理解是:只要保证CLK与DATA到达寄存器的时间一样或不太大就可以了,因为时钟与数据本来就中心对齐了

我看CHIP PLANNER时,发现CLK是通过一个好像叫CLKCTRL的全局时钟BUF再到各寄存器的

这样的话,约束该怎么做?我怎么约束时钟信号到各寄存器的时间,我看对时序约束的说明好像都是知道时钟延时,然后根据公式约束数据通道,但时钟本身的延时呢!

就这么个简单的采集,谁能给说下约束该怎么写吗?

这样是否正确:(adc_clk0是建立的虚拟时钟,240MHz)

create_clock -name {adc_clk0} -period 4.160 -waveform { 0.000 2.080 }

set_input_delay -add_delay -max -clock [get_clocks {adc_clk0}] 1.040 [get_ports {datap}]

set_input_delay -add_delay -min -clock [get_clocks {adc_clk0}] 0.850 [get_ports {datap}]

set_input_delay -add_delay -max -clock_fall -clock [get_clocks {adc_clk0}] 1.040 [get_ports {datap}]

set_input_delay -add_delay -min -clock_fall -clock [get_clocks {adc_clk0}] 0.850 [get_ports {datap}]

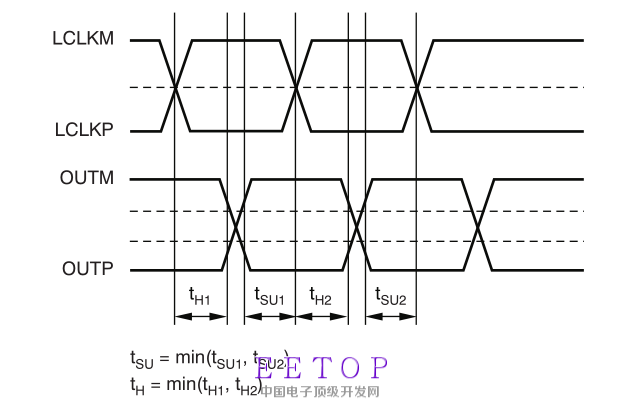

因为是中心对齐,所以我设置了最大为1/2的数据周期,0.85为下图中Th的值

create_clock -name {adc_clk0} -period 4.160 -waveform { 0.000 2.080 }

这个不对,LCLKM明显不是虚拟时钟,要把它和你实际的输入管脚联系在一起。

create_clock -name {adc_clk0} -period 4.160 -waveform { 0.000 2.080 } [get_ports 输入采样时钟管脚名]

set_input_delay/set_output_delay中指定的延迟是根据外部电路计算出的,芯片内部的延迟工具软件是知道的(根据对应的器件参数),这样工具软件就可以用来指导布局布线和做时序分析。

我看资料输入延时用的都是虚拟时钟好像是说这个时钟是别的片子提供的,所以用虚拟时钟

我也觉得应该用端口的真正时钟才对,不清楚资料为什么都说虚拟时钟!

学习学习