xilinx pcie ip仿真 trn_link_up一直不通

ISim P.15xf (signature 0x2f00eba5)

This is a Full version of ISim.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 5 of formal port DFETAP1 is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port GREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port GREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port NORTHREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port NORTHREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port SOUTHREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port SOUTHREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 3 of formal port TXENPRBSTST is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 3 of formal port TXHEADER is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 5 of formal port TXPOSTEMPHASIS is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port TXPRBSFORCEERR is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 4 of formal port TXPREEMPHASIS is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 7 of formal port TXSEQUENCE is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port TXSTARTSEQ is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port USRCODEERR is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port IGNORESIGDET is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port PERFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port PERFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port RXDLYALIGNRESET is not equal to width 32 of actual constant.

WARNING: File "D:/PCIE_TEST_3/pcie/pcie_2_0_v6.v" Line 630. For instance pcie_2_0_i/pcie_bram_i/, width 72 of formal port mim_tx_rdata is not equal to width 69 of actual signal MIMTXRDATA.

WARNING: File "D:/PCIE_TEST_3/pcie/pcie_2_0_v6.v" Line 629. For instance pcie_2_0_i/pcie_bram_i/, width 72 of formal port mim_rx_rdata is not equal to width 68 of actual signal MIMRXRDATA.

WARNING: File "D:/PCIE_TEST_3/pcie/ipcore_dir/v6_pcie_v1_7/example_design/EP_MEM.v" Line 925. For instance EP_MEM/ep_mem_erom/, width 4 of formal port DOPA is not equal to width 1 of actual signal DOPA.

WARNING: File "D:/PCIE_TEST_3/pcie/ipcore_dir/v6_pcie_v1_7/example_design/EP_MEM.v" Line 926. For instance EP_MEM/ep_mem_erom/, width 4 of formal port DOPB is not equal to width 1 of actual signal DOPB.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 5 of formal port DFETAP1 is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port GREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port GREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port NORTHREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port NORTHREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port SOUTHREFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 2 of formal port SOUTHREFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 3 of formal port TXENPRBSTST is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 3 of formal port TXHEADER is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 5 of formal port TXPOSTEMPHASIS is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port TXPRBSFORCEERR is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 4 of formal port TXPREEMPHASIS is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 7 of formal port TXSEQUENCE is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port TXSTARTSEQ is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port USRCODEERR is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port IGNORESIGDET is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port PERFCLKRX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port PERFCLKTX is not equal to width 32 of actual constant.

WARNING: For instance gtx_v6_i/\GTXD[0].GTX /, width 1 of formal port RXDLYALIGNRESET is not equal to width 32 of actual constant.

WARNING: File "D:/PCIE_TEST_3/pcie/pcie_2_0_rport_v6.v" Line 1744. For instance pcie_2_0_i/pcie_bram_i/, width 72 of formal port mim_tx_rdata is not equal to width 69 of actual signal MIMTXRDATA.

WARNING: File "D:/PCIE_TEST_3/pcie/pcie_2_0_rport_v6.v" Line 1743. For instance pcie_2_0_i/pcie_bram_i/, width 72 of formal port mim_rx_rdata is not equal to width 68 of actual signal MIMRXRDATA.

Time resolution is 1 ps

Simulator is doing circuit initialization process.

[ 0] board.EP.core.pcie_2_0_i.pcie_bram_i ROWS_TX 1 COLS_TX 4

[ 0] board.EP.core.pcie_2_0_i.pcie_bram_i ROWS_RX 1 COLS_RX 4

[ 0] board.EP.core.pcie_2_0_i.pcie_bram_i.pcie_brams_tx NUM_BRAMS 4 DOB_REG 1 WIDTH 18 RAM_WRITE_LATENCY 0 RAM_RADDR_LATENCY 0 RAM_RDATA_LATENCY 2

[ 0] board.EP.core.pcie_2_0_i.pcie_bram_i.pcie_brams_rx NUM_BRAMS 4 DOB_REG 1 WIDTH 18 RAM_WRITE_LATENCY 0 RAM_RADDR_LATENCY 0 RAM_RDATA_LATENCY 2

[ 0] board.RP.rport.pcie_2_0_i.pcie_bram_i ROWS_TX 1 COLS_TX 4

[ 0] board.RP.rport.pcie_2_0_i.pcie_bram_i ROWS_RX 1 COLS_RX 4

[ 0] board.RP.rport.pcie_2_0_i.pcie_bram_i.pcie_brams_tx NUM_BRAMS 4 DOB_REG 1 WIDTH 18 RAM_WRITE_LATENCY 0 RAM_RADDR_LATENCY 0 RAM_RDATA_LATENCY 2

[ 0] board.RP.rport.pcie_2_0_i.pcie_bram_i.pcie_brams_rx NUM_BRAMS 4 DOB_REG 1 WIDTH 18 RAM_WRITE_LATENCY 0 RAM_RADDR_LATENCY 0 RAM_RDATA_LATENCY 2

[ 0] : System Reset Asserted...

Finished circuit initialization process.

[ 500000] : test_start.....

ISim> run all

[ 4995000] : System Reset De-asserted...

[ 15917246] : Transaction Reset Is De-asserted...

Stopped at time : 176853150 ps : File "v:/hipsBuilds/P_hips_v05.0/rst/hips/gtxe1/B_GTXE1_enc.v" Line 33061

对了 补充一下,用的是V6的fpga,ip核版本是1.7 dddddd

txd,rxd有信号不 ?

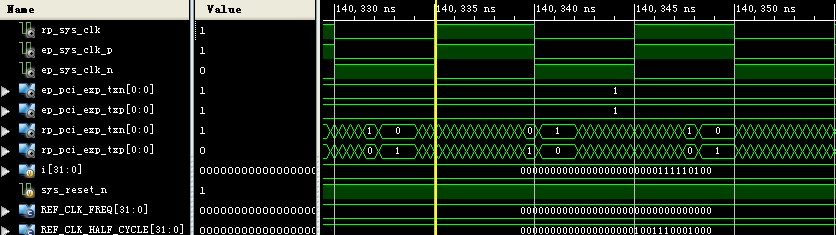

信号如图所示,貌似endpoint端一直是1呢

信号如图,endpoint端一直显示输出1

再补充一下哈,由于它生成的testbench里面有包含的test.v文件,我编译不过,所以我直接把拿一部分直接屏蔽了,直接把test_sample里面的代码直接加进去了,最后是这样的形式,在usrapp_tx文件里面是这样的,这样应该就是直接执行一段测试,不需要再输入指令指定测试内容了吧:

#500 $display("[%t] : test_will_start.....", $realtime);

expect_status = 0;

expect_finish_check = 0;

// Tx transaction interface signal initialization.

trn_td = 0;

trn_tsof_n = 1;

trn_teof_n = 1;

trn_trem_n = 0;

trn_terrfwd_n = 1;

trn_tsrc_rdy_n = 1 ;

trn_tsrc_dsc_n = 1;

// Payload data initialization.

TSK_USR_DATA_SETUP_SEQ;

#550 $display("[%t] : test_start.....", $realtime);

/* //Test starts here

if (testname == "dummy_test")

begin

$display("[%t] %m: Invalid TESTNAME: %0s", $realtime, testname);

$finish(2);

end

//`include "tests.v"*/

//else if(testname == "sample_smoke_test0")

//begin

TSK_SIMULATION_TIMEOUT(10050);

//System Initialization

TSK_SYSTEM_INITIALIZATION;

$display("[%t] : Expected Device/Vendor ID = %x", $realtime, DEV_VEN_ID);

//--------------------------------------------------------------------------

// Read core configuration space via PCIe fabric interface

//--------------------------------------------------------------------------

$display("[%t] : Reading from PCI/PCI-Express Configuration Register 0x00", $realtime);

TSK_TX_TYPE0_CONFIGURATION_READ(DEFAULT_TAG, 12'h0, 4'hF);

TSK_WAIT_FOR_READ_DATA;

if (P_READ_DATA != DEV_VEN_ID) begin

$display("[%t] : TEST FAILED --- Data Error Mismatch, Write Data %x != Read Data %x", $realtime,

DEV_VEN_ID, P_READ_DATA);

end

else begin

$display("[%t] : TEST PASSED --- Device/Vendor ID %x successfully received", $realtime, P_READ_DATA);

end

//--------------------------------------------------------------------------

// Direct Root Port to allow upstream traffic by enabling Mem, I/O and

// BusMstr in the command register

//--------------------------------------------------------------------------

board.RP.cfg_usrapp.TSK_READ_CFG_DW(32'h00000001);

board.RP.cfg_usrapp.TSK_WRITE_CFG_DW(32'h00000001, 32'h00000007, 4'b1110);

board.RP.cfg_usrapp.TSK_READ_CFG_DW(32'h00000001);

$finish;

end

为啥编译不过?是什么样的错误?你先把那部分贴出来看看。

XILINX的库应该已经编译到MODELSIM里了吧?还有${XILINX}变量等设置没问题了?

感谢楼上的回复,我用的是ise自带的isim ,没用modelsim,应该不用编译库 设置变量吧。

没有定义仿真,

换了modelsim,编译了一下xilinx的库,就可以出波形了,谢谢各位的回复

您好,我遇到了和您一样的问题,求指教,我的Q 451719128 万分希望能加下。

trn_lnk_up一直不拉低基本上就是参数定义中没有设仿真的缘故

另外,请教一个问题,怎么使用xilinx生成的example程序仿真CPLD TLP啊?直接使用仿真文件里面的TSK_TX_COMPLETION_DATA的task来发送,设备端好像接收不到CPLD TLP。

在V系列的芯片中,好像需要定义simulation这个函数

如果想发完成包,那么相当于DMA形式,你必须先定义cfg[4]中的寄存器

谢谢!cfg[4]在哪个文件里面?能告诉详细流程吗?定义好cfg[4]中的寄存器,发送TSK_TX_COMPLETION_DATA这个task就可以收到cpld tlp了?再次感谢回复,困扰了很久的问题……

您好!cfg[4]寄存器在哪个文件里面?设置好这个寄存器然后发送TSK_TX_COMPLETION_DATA就可以收到cpld的tlp了?能提供一个详细的接收cpld tlp的流程吗?很感谢!

是配置寄存器,地址为04 具体忘记那个了,你看看,

你用isim仿真的时候,能出波形吗,你系统是64位的吗。我仿真出现如下提示:

ISim O.87xd (signature 0x2f00eba5)

This is a Full version of ISim.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/xilinx_pcie_2_1_ep_7x.v" Line 203. For instance EP/\ext_clk.pipe_clock_i /, width 1 of formal port CLK_RXUSRCLK is not equal to width 8 of actual signal PIPE_RXUSRCLK_IN.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/xilinx_pcie_2_1_ep_7x.v" Line 204. For instance EP/\ext_clk.pipe_clock_i /, width 8 of formal port CLK_RXOUTCLK_OUT is not equal to width 1 of actual signal PIPE_RXOUTCLK_IN.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/pcie_pcie_top.v" Line 752. For instance pcie_top_i/axi_basic_top/, width 7 of formal port trn_rbar_hit is not equal to width 8 of actual signal trn_rbar_hit.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/pcie_pcie_7x.v" Line 353. For instance pcie_7x_i/pcie_block_i/, width 128 of formal port TRNTD is not equal to width 64 of actual signal trn_td.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/pcie_pcie_7x.v" Line 354. For instance pcie_7x_i/pcie_block_i/, width 2 of formal port TRNTREM is not equal to width 1 of actual signal trn_trem.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/pcie_pcie_7x.v" Line 547. For instance pcie_7x_i/pcie_block_i/, width 128 of formal port TRNRD is not equal to width 64 of actual signal trn_rd.

WARNING: File "E:/ISE/kc705_pcie_20140226/ipcore_dir/pcie/simulation/functional/pcie_pcie_7x.v" Line 548. For instance pcie_7x_i/pcie_block_i/, width 2 of formal port TRNRREM is not equal to width 1 of actual signal trn_rrem.

ERRORortability:3 - This Xilinx application has run out of memory or has

encountered a memory conflict. Current memory usage is 2093456 kb. You can

try increasing your system's physical or virtual memory. If you are using a

Win32 system, you can increase your application memory from 2GB to 3GB using

the /3G switch in your boot.ini file. For more information on this, please

refer to Xilinx Answer Record #14932. For technical support on this issue,

you can open a WebCase with this project attached at

http://www.xilinx.com/support.

ERROR: The simulation failed to launch for the following reason:

The Simulation shut down unexpectedly during initialization. Please review the ISim log (isim.log) for details.

Please shut down ISim and retry the simulation. If the problem persists, please contact Xilinx support.

Time resolution is 1 fs

No active Database

Unable to execute live simulation command.

The simulation has terminated.

还望指教,多谢

ERRORortability:3 - This Xilinx application has run out of memory or has

encountered a memory conflict. Current memory usage is 2093456 kb. 仿真有这么占资源吗

用modelsim出来结果了,isim一直提示超出内存,这东西这么占内存啊,别人用isim仿真都是用的64位系统吗,感谢楼上的讨论

原来这样哦

引用 “在xilinx的网站上以“trn_lnk_up_n”为关键字搜索,搜到“In simulation, signal "trn_lnk_up_n", is always deasserted. How can I do?”这个标题,便是解决办法。”

您好,我想请教一下,您说的“没有定义仿真,”是什么意思? 该怎样定义呢?

谢谢

还是有高手的!

不运行do文件怎么进行仿真啊,求教