用ise和modelsim做系统时序仿真,单比特数据的问题

时间:10-02

整理:3721RD

点击:

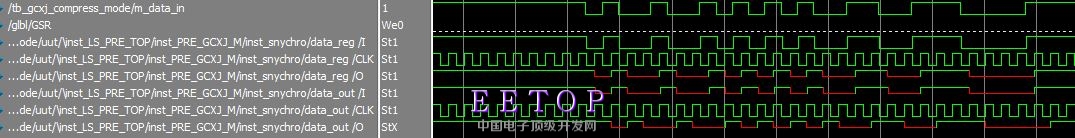

如题,在用ISE和modelsim做时序仿真,加入单比特数据信号,结果发现数据的高电平是正常的,而低电平是红色的,这是为什么?

之前进行过功能仿真,所有的功能都能够正确实现,没有问题。现在是在上板测试后发现有数据传输错误,需要进行问题定位,因为项目背景原因,必须保证设计的可靠性和稳定行,所以要进行对设计的整体时序分析 。求大神指导!

tb中产生串行的数据,然后在作为输入信号,在第一个模块对输入的串行数据进行串并变换成为并行数据。问题就在对输入的串行数据分析时出现低电平是红色的问题。贴上截图如下

在加入打拍信号的rst信号发现,rst是最开始出现红色错误,然后再打拍的always模块中去掉rst信号和对信号的初始化,之接进行打拍输出,仿真结果gate信号和data信号都变为正常。

我的疑问是: 这个为什么这样修改rst信号,仿真的结果就正常了?为什么rst信号会对仿真有这么大影响?在做设计时rst信号要注意什么,满足什么要求?

其中的data_out是时钟上升沿将data_reg输出的数据

以data信号为例

原代码如下:

always @(negedge clk or posedge rst)begin

if(rst)begin

data reg<= 1'b0 ;

data_out <= 1'b0;

end

else begin

data reg<= data_in ;

data_out <= data_reg;

end

end

修改后的代码如下:

always @(negedge clk or posedge rst)begin

data reg<= data_in ;

data_out <= data_reg;

end

求各位前辈指点小弟;感激不尽!

希望大家多多知道,谢谢了!

多多指点