一直都不太明白Verilog不完整的if语句会产生锁存器,前辈筒子们杀进来。

,是不是应该第二个也即电平触发才会有锁存器出现?

,是不是应该第二个也即电平触发才会有锁存器出现?还有一个问题,不完整的if会产生锁存器,那如果就是满足条件才动作,否则保持该咋处理?

谢谢各位了,/鞠躬

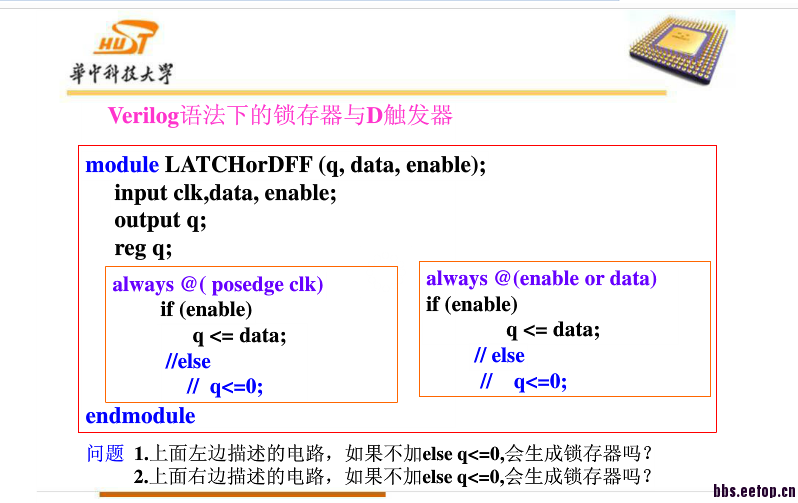

1、时序电路,生成触发器,触发器是有使能端的,使能端无效时数据不变,这是触发器的特性。

2、组合逻辑,由于数据要保持不变,只能通过锁存器来保存。

小编位的第二个代码就是在enable为低时,数据不变,因此要生成锁存器。

第一个代码,由于是时序逻辑,生成的触发器在enable无效时就可以保存数据。跟锁存器无关。

俺也不确定,求高手解答!

多谢啊。还有点不很清楚,那是不是意味着如果要保持数据,不完整的if在组合及时序中都是可以的(能实现所需逻辑功能)?只不过组合的情况下产生的锁存器会有些浪费资源?

2楼正解

两个LATCH串联不就是触发器吗? 搂猪的问题可以说是综合成一个还是二个锁存器的问题.

latch其实比dff结构更简单啊

数字设计中如果你能控制好时序,有意识地用latch也不是不可以。但同时也会增加后面时序分析的工作量。前端设计与后端时序分析要传递的信息量比较多,也容易遗漏,但也可以做好。

就怕无意识地用了latch,例如本想实现一个组合逻辑功能,却因为条件没有写完备导致出现了latch,后端再一疏忽,导致完全不可控。

而用dff实现数据保持的功能,问题就简化多了

明白了,十分感谢你

2楼、7楼正解呀。

呵呵,第一个是寄存器,第二个正常时mux

第二个正常没存储功能,漏写条件,由于电平触发会生成不需要的latch

学习了!

学习了,多谢!

带时序的一般综合出来的是触发器

组合逻辑,if或case不完备,会综合出来锁存器

if语句没有else会产生锁存器这句话本身有歧义,个人觉得没有说明白。就想你的程序1,它本身就是个DFF,怎么就算不写else也不会产生latch;第二个程序肯定会产生latch。

tks

l learn a lot

仔细看看 D触发器 内部结构。 是由几个 RS 或 JK 触发器构建的。

else

; //加个空语句,据说这样可以避免产生latch

你的意思是不是在时序逻辑中,if语句不完整的话,相当于在else部分保存原值,但是不会生成锁存器?

锁存器会增加时序分析的难度,一般不建议使用

个人理解: 所谓生成latch其实是针对使用always语句描述一个组合逻辑而言,因为如果描述时序逻辑总是使用时钟或者时钟+复位作为敏感列表条件,所生成的电路总是组合逻辑+DFF;如果是描述组合逻辑,敏感列表中必然没有时钟复位,而是组合逻辑的输入信号。在FPGA设计,避免使用latch,不利于时序分析和仿真。 楼上有提到latch比DFF省资源, 这个在FPGA设计中其实还好, 因为在FPGA中DFF就是一个专用的硬件资源,并且数量也比较多。

使用always描述组合逻辑时,好的习惯是使用always @(*)作为敏感列表, 并且需要检查每个分支都有明确的赋值,从而避免生成latch.

学习了

学习了

学习了

第1句表述是不是有误

如果第一种情况中没有使能端,只是简单的边沿触发的触发器,应该也会生成锁存器?还是说沿触发的就稳定不会产生锁存器,(因为其有自动保持功能),而电平触发的不能自动保存数据,因此就会生成锁存器?

我是这么理解的,在一份资料看的,

时序电路=组合逻辑电路+储存电路;

储存电路有两个:锁存器(latch)和触发器;

边沿触发产生触发器,

电平触发产生锁存器,

多个触发器组成寄存器,

当描述的是时序电路,寄存器变量对应的寄存器,

描述的是完整的组合逻辑电路,对应为硬件连线,

当描述的是不完整组合逻辑,则寄存器对应的是锁存器;