关于ADC的采样频率,求解啊

时间:10-02

整理:3721RD

点击:

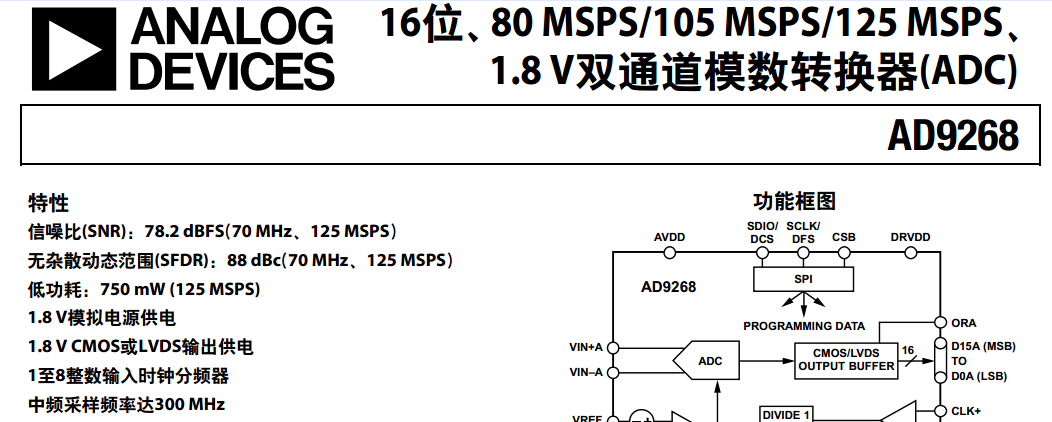

[attach]586565[/attach]请问:

如上图datasheet所示

信噪比(SNR):78.2dBFS(70MHz,125MSPS) 里的70MHZ是指什么?125MSPS是不是就是指这款ADC的采样频率?

中频采样频率达300MHz 又怎么解释?

麻烦大神回答下,感激不尽!

[attach]586567[/attach]

70M是指输入中频信号的频率,125MSPS是指采样频率,在这个条件下的SNR=78.2dBFs

300MHz是指这款ADC可以最大输入的中频信号频率

噢~谢谢你的回答

学习。

哈哈,还是有高手的

3楼答案。

good information

good information

答案是对的

答案是对的。