用Chipscope抓取信号出现问题

时间:10-02

整理:3721RD

点击:

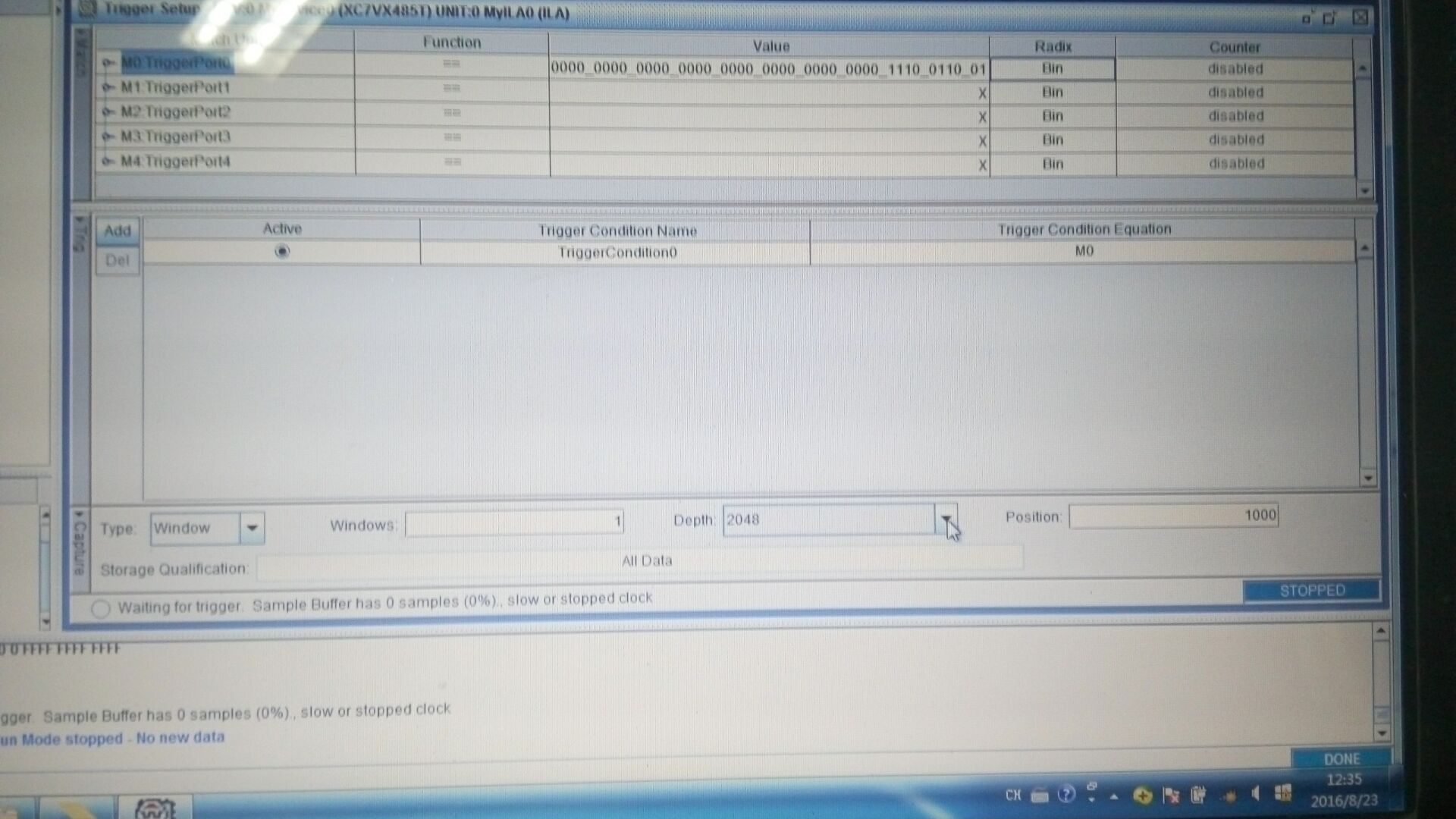

我是用chipscope抓取信号PLI_filtered,设置的触发条件是44位的PLI_filtered数值达到3086时触发,然后左下角会出现waiting for trigger,sample buffer has 0 samples,slow or stopped clock

请大家来帮帮忙,第一次用chipscope,不知道这是什么地方出了问题

没有时钟了

你的clk频率是多少?

clk有没有进行管脚约束?

说明没达到触发条件

没有触发,条件不满足

谢谢大家,是触发信号设置的有问题