Xilinx 7系列FPGA使用之CLB探索

时间:10-02

整理:3721RD

点击:

7系列FPGA是Xilinx新推出的基于28nm工艺的FPGA,其中包含三个系列:Artix、Kintex和Virtex。因项目要使用kintex7为平台做设计,需要对其内部结构做了研究,首先从CLB(Configurable Logic Block)开始:

CLB构成了Kintex7主要逻辑单元,其中包含2个Slice,并且Slice分为2种:SLICEL和SLICEM,SLICEL为普通的Slice逻辑单元,而SLICEM在基本逻辑功能的基础上可以扩展为分布式RAM或者移位寄存器。在所有Slice资源中,有2/3是SLICEL,因此一个CLB可以有2个SLICEL或者1个SLICEL、1个SLICEM组成。

如图1所示为SLICEM的内部结构,其中包含4个6输入LUT(红色圈)、进位链(黄色圈)、多路复用器(蓝色圈)和8个寄存器(绿色圈)。

图1

6-input LUT:此处LUT沿用了Xilinx 6系列FPGA的6输入LUT结构,6-input LUT内部是由2个5-input LUT组成,有两个输出分别对应O¬6和O5。在设计中,如果综合后有2个5-input LUT需要是使用,如果在ISE将综合选项-lc(LUT Combining)设置成Area,综合器XST会将这2个5-input LUT合并在一个6-input LUT中实现,但是此选项相当于以速度换面积,随之逻辑延时将增大。

寄存器:此处Xilinx区别于Altera器件,其1个LUT对应了2个register,而Altera器件中是一一对应的。从图中可以发现,第2列的register比第1列多了FF/LAT这个选项,这表示第1列的register只能作为Flip-Flop使用,而第2列的register既能作为Flip-Flop也能作为Latch使用。另外还有INIT0、INIT1、SRLO和SRHI 四个选项,其中INIT0和INIT1配对,表示通过GSR全局复位/置位,此复位/置位网络为异步的;而SRLO和SRHI配对,表示高电平有效信号SR驱动的复位/置位,此信号可以配置成异步或者同步,但这8个register共用一个SR信号,因此其方式必须相同,根据此特性,建议写代码时,复位/置位方式选择同步高电平有效。

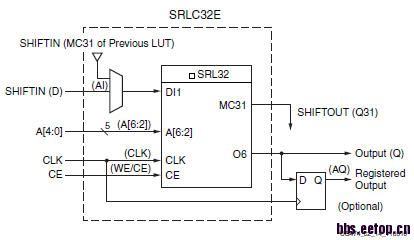

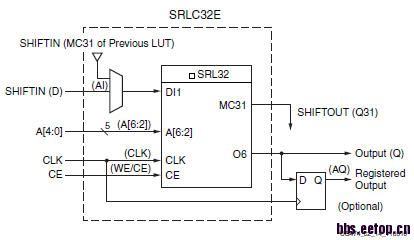

下面对SLICEM做一下重点说明,其可扩展成移位寄存器,如图2所示,Slice中的每个LUT可配置成32-bit的Shift Register,因此1个Slice最多可扩展成128-bit的Shift Register。其操作模式为1个时钟周期移1为,通过D输入端输入,并且最后1位通过MC31输出,并且可以以A[6:2]作为5位地址选择O6输出32位中的某一位进行输出。

图2

在写代码时,可以按规范写出移位寄存器的形式,如以下代码所示:

图3

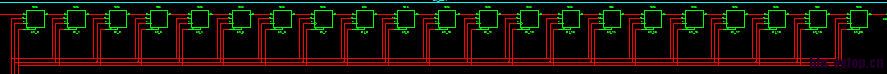

如按一下代码进行综合后得到结构如图4所示,综合器使用了21个FF实现了这个21-bit移位寄存器,则需要21个Slice。

图4

为什么综合器会产生不同的结构?分析一下代码的区别,第二段代码相比于第二段代码多了一个同步复位功能,而根据SLICEM的结构,其中的LUT是没有同步复位控制输入端的,因此综合器无法将代码综合成想要的结构,因此写代码时需要根据相应的结构来编写。

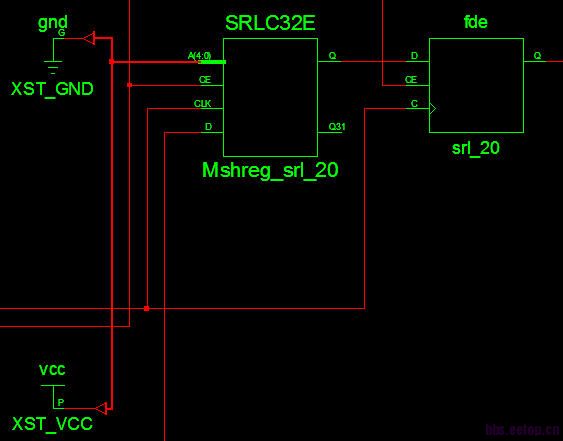

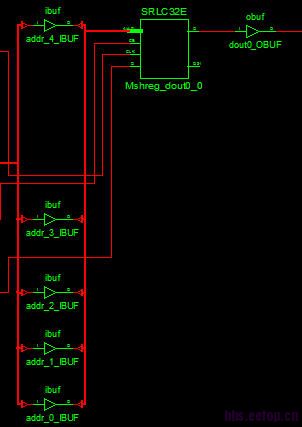

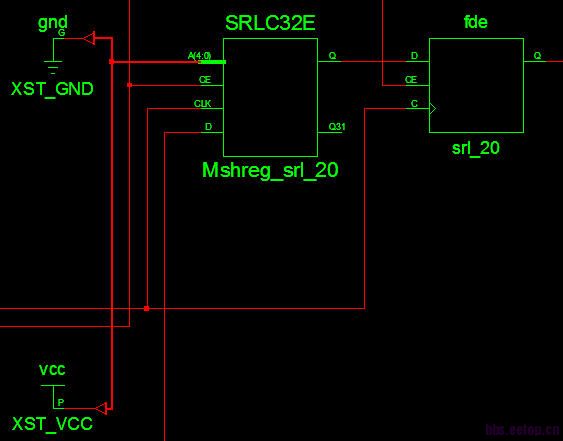

观察图3可以发现,在SRLC32E输出端Q后又接入了一个FF作为同步输出,查手册后发现,此移位寄存器可以配置成两种输出模式:静态地址方式和动态地址方式,这两种模式的不同之处在于静态地址方式是同步输出,图3中结构是静态地址方式;而动态地址方式是异步输出,即没有后接FF直接从SRLC32E的Q端输出,以下代码表示动态地址方式,其中addr是一个变量。

图5

CLB构成了Kintex7主要逻辑单元,其中包含2个Slice,并且Slice分为2种:SLICEL和SLICEM,SLICEL为普通的Slice逻辑单元,而SLICEM在基本逻辑功能的基础上可以扩展为分布式RAM或者移位寄存器。在所有Slice资源中,有2/3是SLICEL,因此一个CLB可以有2个SLICEL或者1个SLICEL、1个SLICEM组成。

如图1所示为SLICEM的内部结构,其中包含4个6输入LUT(红色圈)、进位链(黄色圈)、多路复用器(蓝色圈)和8个寄存器(绿色圈)。

图1

6-input LUT:此处LUT沿用了Xilinx 6系列FPGA的6输入LUT结构,6-input LUT内部是由2个5-input LUT组成,有两个输出分别对应O¬6和O5。在设计中,如果综合后有2个5-input LUT需要是使用,如果在ISE将综合选项-lc(LUT Combining)设置成Area,综合器XST会将这2个5-input LUT合并在一个6-input LUT中实现,但是此选项相当于以速度换面积,随之逻辑延时将增大。

寄存器:此处Xilinx区别于Altera器件,其1个LUT对应了2个register,而Altera器件中是一一对应的。从图中可以发现,第2列的register比第1列多了FF/LAT这个选项,这表示第1列的register只能作为Flip-Flop使用,而第2列的register既能作为Flip-Flop也能作为Latch使用。另外还有INIT0、INIT1、SRLO和SRHI 四个选项,其中INIT0和INIT1配对,表示通过GSR全局复位/置位,此复位/置位网络为异步的;而SRLO和SRHI配对,表示高电平有效信号SR驱动的复位/置位,此信号可以配置成异步或者同步,但这8个register共用一个SR信号,因此其方式必须相同,根据此特性,建议写代码时,复位/置位方式选择同步高电平有效。

下面对SLICEM做一下重点说明,其可扩展成移位寄存器,如图2所示,Slice中的每个LUT可配置成32-bit的Shift Register,因此1个Slice最多可扩展成128-bit的Shift Register。其操作模式为1个时钟周期移1为,通过D输入端输入,并且最后1位通过MC31输出,并且可以以A[6:2]作为5位地址选择O6输出32位中的某一位进行输出。

图2

在写代码时,可以按规范写出移位寄存器的形式,如以下代码所示:

- always@(posedge clk)

- if(clk_en)

- srl<={srl[31:0],din};

- assign dout0=srl[20];

图3

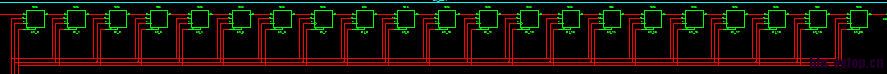

如按一下代码进行综合后得到结构如图4所示,综合器使用了21个FF实现了这个21-bit移位寄存器,则需要21个Slice。

- always@(posedge clk)

- if(rst)

- srl<=32’d0;

- else

- if(clk_en)

- srl<={srl[31:0],din};

- assign dout0=srl[20];

图4

为什么综合器会产生不同的结构?分析一下代码的区别,第二段代码相比于第二段代码多了一个同步复位功能,而根据SLICEM的结构,其中的LUT是没有同步复位控制输入端的,因此综合器无法将代码综合成想要的结构,因此写代码时需要根据相应的结构来编写。

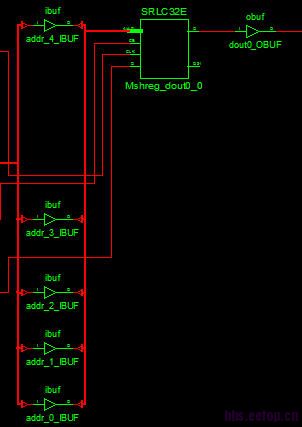

观察图3可以发现,在SRLC32E输出端Q后又接入了一个FF作为同步输出,查手册后发现,此移位寄存器可以配置成两种输出模式:静态地址方式和动态地址方式,这两种模式的不同之处在于静态地址方式是同步输出,图3中结构是静态地址方式;而动态地址方式是异步输出,即没有后接FF直接从SRLC32E的Q端输出,以下代码表示动态地址方式,其中addr是一个变量。

- always@(posedge clk)

- if(rst)

- srl<=32’d0;

- else

- if(clk_en)

- srl<={srl[31:0],din};

- assign dout0=srl[addr];

图5

在对7系列进行RTL设计时,要和以前的版本有所区别才能达到最优啊。

但是基本还是沿用了V6的逻辑结构!

和V6、V5差别不大,体系结构基本相同,工艺改进了

xuexizhong

非常感谢

确实和V6差别不是太大

需要的時候深入研究,否則依賴工具即可。

KDHFJADHFJKKCNMDS

xie xie xie xie xie xie

多给点教程

不错不错!

very good

在对7系列进行RTL设计时,要和以前的版本有所区别才能达到最优啊

最近在用V6,觉得没什么区别。

倒是V6、V7相对于V4、V2差别蛮大的。

布线布局的效率如何?

kankan

kankan

非常感谢

re!

受教学习ing

hehao heqiangda

在ZYNQ,值得参考!

体系结构基本相同,看来V5还可以顶着用几年先

学习了,不错

好高深,貌似看不懂

在对7系列进行RTL设计时,要和以前的版本有所区别才能达到最优啊。

但是基本还是沿用了V6的逻辑结构!

这篇文章很有意义

顶顶顶顶