XILINX chipscope 波形问题!新人求助

时间:10-02

整理:3721RD

点击:

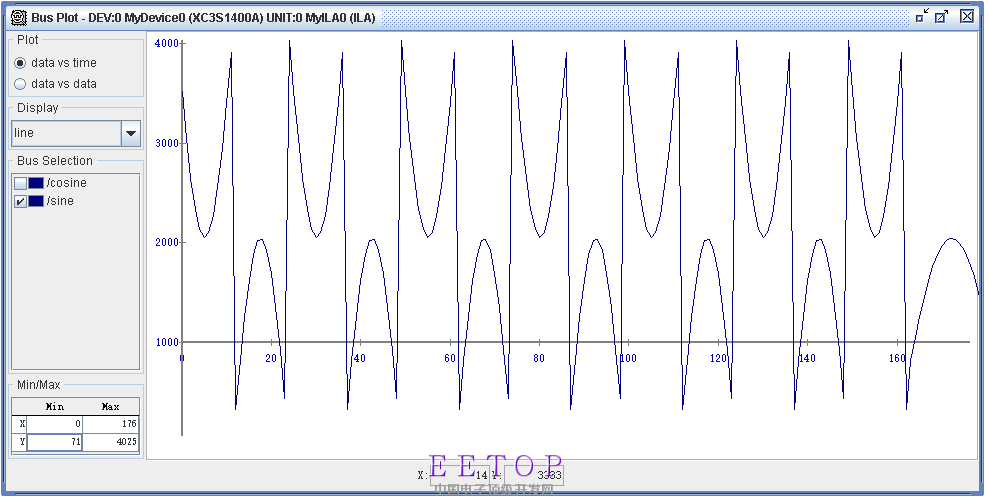

我根据按照书上例程自己构建PROJIECT产生一个单通道信号发生器,出来的波形是这样的[attach]639195[/attach]

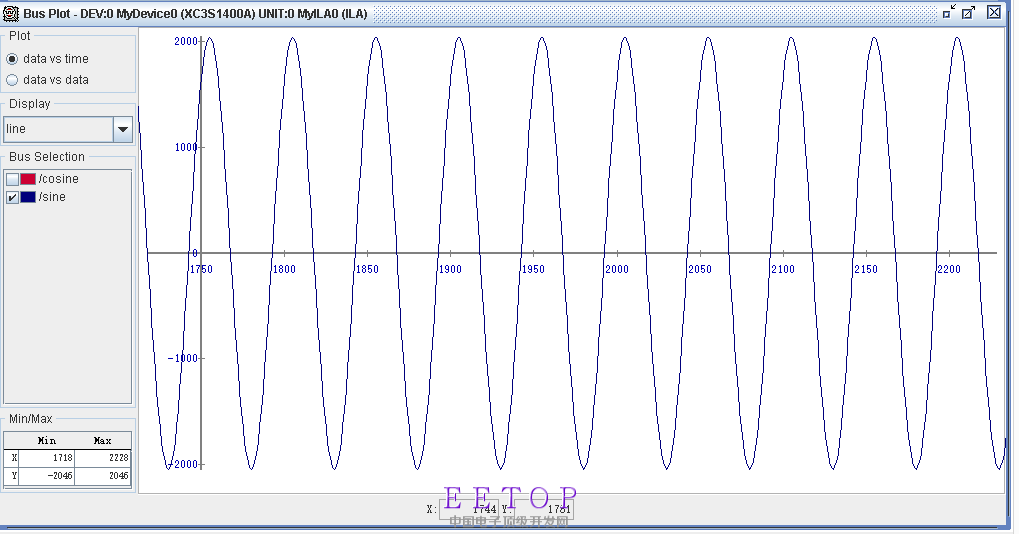

直接用书上的资料代码出来的波形是这样的

不知道哪里出问题了,是漏了哪步吗?求大神指教!基本上配置都一模一样,除了芯片型号不一样。

附上verilog:

module dds_1(mclk, sine, cosine

);

input mclk;

output [11 : 0] sine;

output [11 : 0] cosine;

reg we = 0;

reg [25:0] data = 0;

reg [25:0] data1 = 0;

reg [12:0] cnt = 0;

always @(posedge mclk)

begin

cnt <= cnt + 1;

if(cnt[12] == 1)

begin

data1 <= 1342177;

end

else

begin

data1 <= 2684354;

end

end

always @(posedge mclk)

begin

data <= data1;

if(data == data1)

we <= 0;

else

we <= 1;

end

dds_11 inst_dds_11 (

.clk(mclk), // input clk

.we(we), // input we

.data(data), // input [25 : 0] data

.cosine(cosine), // output [11 : 0] cosine

.sine(sine) // output [11 : 0] sine

);

endmodule

数据格式在ChipScope里设置为有符号数

晓得了,哎,一直没用过这个模式!

谢谢,果然就好了~感谢大神!

路过,学习了