产生翻转信号

时间:10-02

整理:3721RD

点击:

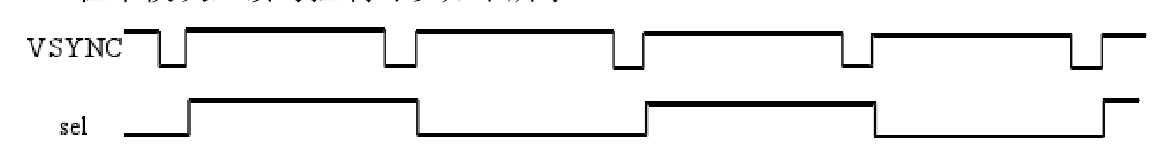

想问下,在没有时钟的情况下,可以通过信号vsync 产生sel信号吗?

今天试了很久都没能够得到,后来加了个时钟,发现并不能得到想要的波形,而且sel波形受时钟变化的影响。谢谢大家!

可以的,用vsyns当时钟

always @ (posedge vsync or negedge rst_n)

begin

if (!rst_n)

sel <= 1'b0 ;

else

sel <= #DLY ~sel ;

end

谢谢,但是vsync不是敏感信号,需要一个标识判定上升沿。

用D触发器加一个反相器就可实现

没有时钟,D触发器有什么用?

什么叫敏感信号?这个sel就是用sync上升沿触发锁出来的

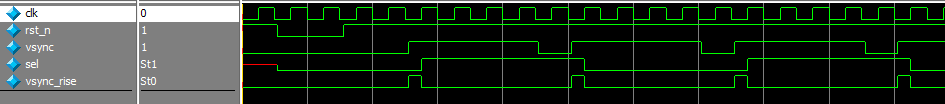

- module edge_detect(

- input clk,

- input rst_n,

- input vsync,

- output reg sel

- );

- reg vsync_r1;

- always @(posedge clk or negedge rst_n)

- if(!rst_n)

- vsync_r1 <= 1'b0;

- else

- vsync_r1 <= vsync;

- wire vsync_rise = vsync && (!vsync_r1);

- always @(posedge clk or negedge rst_n)

- if(!rst_n)

- sel <= 1'b0;

- else if(vsync_rise)

- sel <= !sel;

- endmodule

什么敏感信号?你没有其他时钟,只能将vsync当成时钟使用了。

that's a pretty smart idea.

我这样写过,感觉sel 信号是受CLK信号影响,