关于寄存器在上电时的初值问题?

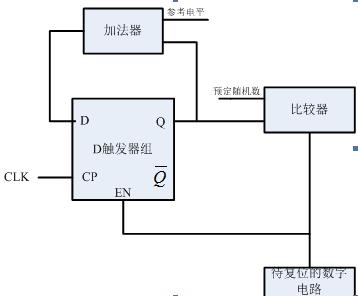

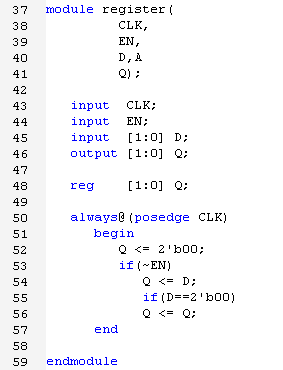

经过分析,是由于寄存器在时钟上升沿到来时没有先赋初值0,寄存器组的程序如下:

我想问的问题是,这个程序有问题吗?如果有问题,那么该如何给Q一个初值?

(【注】:整个数字上电复位只有一个输入一个输出,输入是时钟信号CLK,输出是上电复位信号POR)

求大神们给给建议……谢谢……

复位后给寄存器赋初始值

关键是这个电路就是为了在上电后产生一个复位信号,输入就是一个CLK,没有复位rst,所以……

不懂。期待大神回答。

没有做过ASIC。这种代码风格也不喜欢,我觉得写FPGA代码越细越好,不怕啰嗦,每一个if else都写的清清楚楚的,这样有时候都很难保证综合出来的结果是自己想要的。更何况写的这么。抽象?呵呵

数字电路真正原始的上电复位,是来自于模拟的电压比较器,其原理是电源电压高过参考电压一段时间后,发出一个表明电源ready的信号,这个信号的产生是纯模拟器件,不要要用到任何寄存器。

如果你没有这样的复位源,可以用来自pin上的复位,就是按键reset。

模拟会产生一个复位的

我怎么看着你的Q除了2'b00还是2'b00呢

还有 你的 if(~EN) 与后面的if到底有没有关系?

我感觉你是太懒以至于丢了begin end

代码风格看着很捉急

在后仿的TB里 deposit 一个random值 于Q ?

过来学学!

always@(posedge)

begin

Q = 2‘b00;

if(~EN)

begin

Q <= D;

end

else

begin

Q <= Q;

end

end

因为在Q输出为11时,比较器输出为1,此时EN端无效,就自动执行Q保持的功能了。

代码风格确实有所欠缺,sorry。

最后,其实我想问的是前面这句: Q = 2‘b00。我觉得这么写有问题,但是前仿又可以通过,。我也是醉了。

什么意思?可以具体说说吗?

想用数字寄存器产生上电复位信号,而产生复位信号的这个寄存器自己的复位如何来?呵呵,这个似乎只有理论研究意义,没有什么实际价值。

这只是用于仿真,给寄存器赋初值。解决某些寄存器没有复位信号在你的testbench里面加上:

$deposit(xxxxx.Q, 2'b0);

只能解决仿真时寄存器没有初始化的问题

$deposit(xxxx.Q, 2'b0);

如果这样写,Q<= 2‘b00完全可以去掉,因为无论如何都会被后面的Q赋值覆盖掉

【链接:http://www.freepatentsonline.com/result.html?sort=relevance&srch=top&query_txt=DIGITAL+POWER+ON+RESET&submit=&patents=on】

但是你说的不无道理,因为数字电路要工作,寄存器要工作,其必须达到有效电平,要是没有上电,寄存器就不会工作,就不谈复位了。但是,从另一方面来讲,数字电路可以在上电完成后立即进行复位嘛……

我的意思是说,在工程角度看,任何芯片中,模拟一定有这样一个稳定可靠的上电复位信号存在的,数字故意不用它,另辟蹊径大费周章自己设法去产生这样的信号,意义在哪里。这就是抛开实际只谈理论研究呀。

感觉完全没有入门啊

always @(posedge clk or negedge EN)

if (!EN)

Q <= 1'b0;

else

Q <= adder_output

不用 Q <= Q,本来寄存器就能保持原值