ISE14.3 利用Block RAM生成的IP核,输出信号为什么是不定值?

时间:10-02

整理:3721RD

点击:

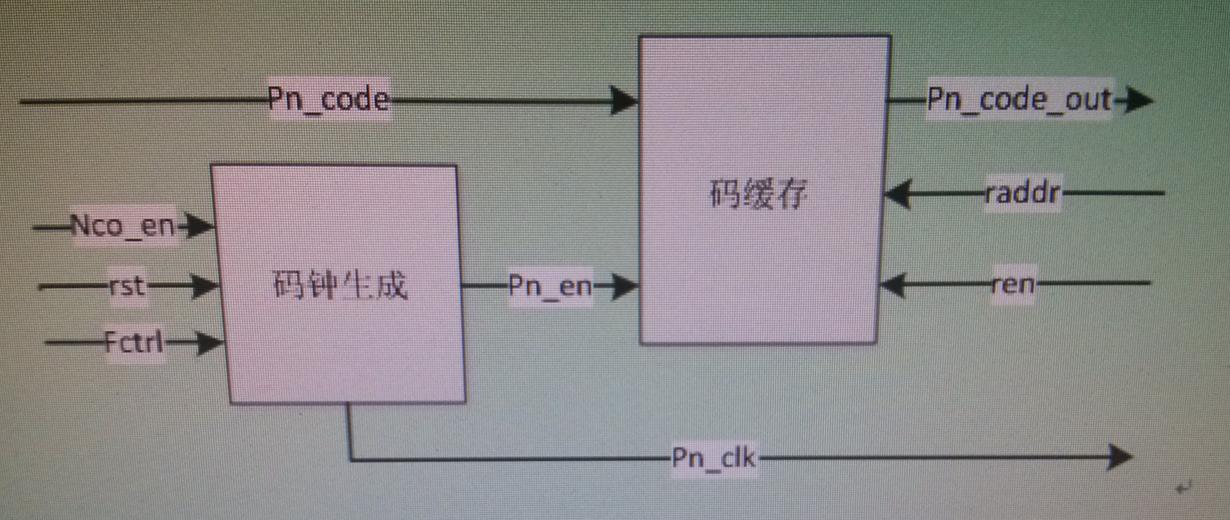

首先,我是利用NCO生成原始的脉冲信号(Pn_en),再用脉冲信号作为新生成RAM的写使能(wena)。pn_code是输入信号,waddr_gen模块产生地址信号。现在我假定pn_code=8'hFF; pn_en按照码钟生成模块的时序输入,为什么我的码缓存(D_RAM)输出为不定值呢?

[attach]660536[/attach]

[attach]660536[/attach]

想了很久也没有明白,希望能得到大家的帮助!

[attach]660536[/attach]

[attach]660536[/attach]

想了很久也没有明白,希望能得到大家的帮助!

把RAM另一侧的写使能,地址,数据抓出来看看有没有写进去

我的RAM核是单口的,而且我这里只用了写入的功能。waddr的地址计数功能正常,但是就是找不到为什么Pn_code_out为什么输出不定值。时序图都没有看全啊,读使能在哪里?

我暂时还没有写读出的部分代码。我是先把信号写进来,想在isim里面看看我的信号是否写入。先检查你的复位信号和读写使能信号有没有做反,到底高有效还是低有效?

如果上面没问题,你的波形图显示的是写操作,有些RAM设计的数据输出口是不会随着写动作而变化的,你要给个读操作再看看数据输出口。

你这样是看不出来的啊,只有读信号产生了才会有输出读,才知道有没有写进去啊

楼上说的对。

想看数据是否写进RAM,从写端怎么看?

对于写,我们需要做的是,看是否满足写RAM所需要的时序,

至于验证,你没有写读的代码,我还真不知道怎么验证。我是刚学FPGA的新手,谢谢大家的热心建议,单口生成的ram核里面没有发现可以读的端口...

我找到为什么输出不定值的原因了,由于输出是被例化过的,我的输出信号没定义为wire类型,所以才会输出不定值。