关于spartan6下DDR2的操作,可以看一下我的博客。

吉他哥,那个MIG生成的ddr控制器我当做子模块,加上一个循环读写测试模块,然后封装在top顶层模块内就会报错::ConstraintSystem:58 - Constraint <NET

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/selfrefresh_mcb_mode" TIG;> [mig_37.ucf(36)]: NET

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/selfrefresh_mcb_mode

" does not match any design objects.

ERROR:ConstraintSystem:58 - Constraint <INST

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/gen_term_calib.mcb_soft_calibration_top_inst/mcb_soft_calibration_inst/DONE_SOFTANDHARD_CAL*"

TIG;> [mig_37.ucf(38)]: INST

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/gen_term_calib.mcb_s

oft_calibration_top_inst/mcb_soft_calibration_inst/DONE_SOFTANDHARD_CAL*"

does not match any design objects.

ERROR:ConstraintSystem:58 - Constraint <NET

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/gen_term_calib.mcb_soft_calibration_top_inst/mcb_soft_calibration_inst/CKE_Train" TIG;>

[mig_37.ucf(43)]: NET

"memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/gen_term_calib.mcb_s

oft_calibration_top_inst/mcb_soft_calibration_inst/CKE_Train" does not match

any design objects.

ERROR:ConstraintSystem:59 - Constraint <NET

"memc3_infrastructure_inst/sys_clk_ibufg" TNM_NET = "SYS_CLK3";>

[mig_37.ucf(57)]: NET "memc3_infrastructure_inst/sys_clk_ibufg" not found.

Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file.

ERROR:NgdBuild:924 - input pad net 'c3_sys_clk' is driving non-buffer

primitives:

如果用MIG生成的控制器当做顶层模块,循环读写测试模块在控制器内部实现,那么就可以,这是为什么啊?难道mig生成的控制器只能当顶层模块,不能当子模块吗?

可以当底层,把uCF那部分删掉就可以了,不影响的

##################################################################################

# Timing Ignore constraints for paths crossing the clock domain

##################################################################################

NET "memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/selfrefresh_mcb_mode" TIG;

NET "c?_pll_lock" TIG;

NET "memc?_wrapper_inst/mcb_ui_top_inst/mcb_raw_wrapper_inst/gen_term_calib.mcb_soft_calibration_top_inst/mcb_soft_calibration_inst/CKE_Train" TIG; ##This path exists for DDR2 only

############################################################################

## Memory Controller 3

## Memory Device: DDR2_SDRAM->MT47H64M16XX-25

## Frequency: 312.5 MHz

## Time Period: 3200 ps

## Supported Part Numbers: MT47H64M16HR-25

############################################################################

############################################################################

## Clock constraints

############################################################################

NET "memc3_infrastructure_inst/sys_clk_ibufg" TNM_NET = "SYS_CLK3";

TIMESPEC "TS_SYS_CLK3" = PERIOD "SYS_CLK3" 3.2 ns HIGH 50 %;

############################################################################

您说的是删掉这部分的约束吗?

好贴要顶。

shi

用MIG生成的DDR2控制器工作时会重新校正初始化。

我将初始化完成信号用LED显示,发现有灭又亮的情况,就是DDR2控制器又重新初始化了,谁知道是哪些原因引起的呢?先谢谢各位了~

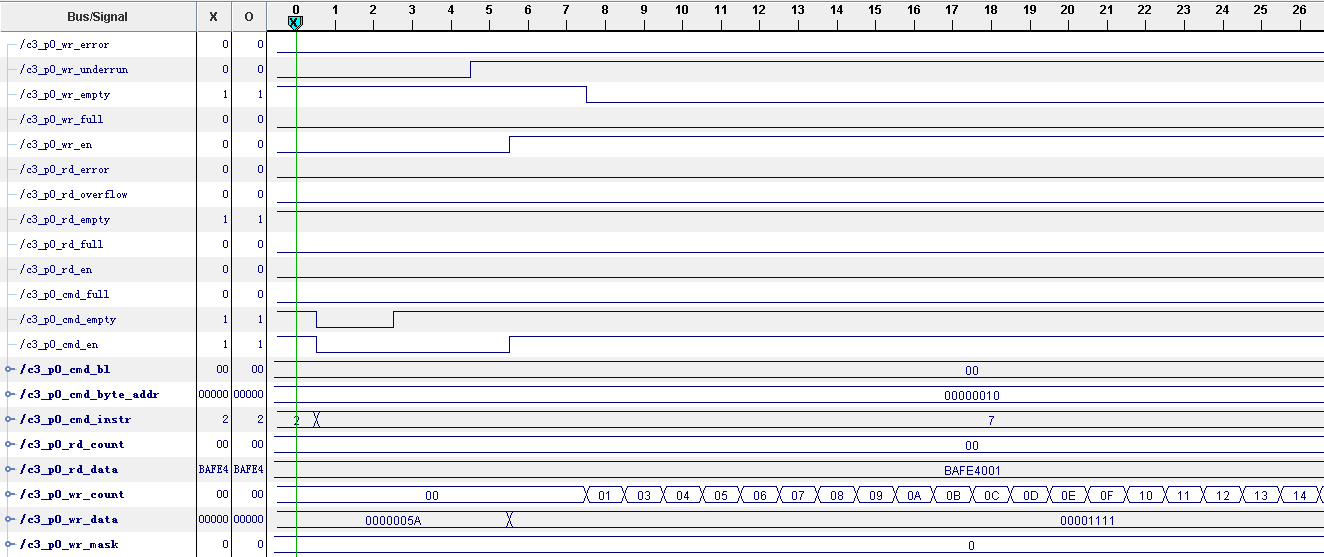

吉他哥,为什么我的wr_underrun信号一直是高电平啊,是哪个时序不对吗?

电源这些供电稳定吗?纹波大约多少 ?还有复位信号怎么弄呢?

这个信号还真的忘记了,读写正常不?

文波两百多毫伏

复位信号外接一个按键

是我的时序理解错了,按照手册上的来,就搞对了,不过手册的时序还是不详细!

吉他哥又得麻烦你了,工程中建立好之后,我暂时没有进行管脚分配,编译的时候在map过程中会报错,我从pll中分出了二个时钟输出给外部管脚,之前一直报错后来加上ODDR2+OBUF然后输出给外部,但是我在map的时候一直报ERRORack:1107 - Pack was unable to combine the symbols listed below into a

single IOB component because the site type selected is not compatible.

的错误,不知道为什么。难道我的ODDR2和OBUF用多了?还是别的原因?补充:我的UCF文件管脚约束文件一直没有加!因为我暂时没有进行管脚分配!

这个问题忘记了,但是这样用是没有问题的我当时也是用DDR2的时钟来分频作为全局时钟的

感觉电压的缘故

先顶一个,进去看看那

先顶一个,进去看看那

谢谢分享

你好,帖子地址已经找不到了。

我在使用MIG的时候,map出现如下错误:

Place:866 - Not enough valid sites to place the following IOBs:

IO Standard: Name = LVCMOS25, VREF = NR, VCCO = 2.50, TERM = NONE, DIR = BIDIR, DRIVE_STR = 12

IO

This may be due to either an insufficient number of sites available on the device, too many prohibited sites,

or incompatible I/O Standards locked or range constrained to I/O Banks with valid sites.

This situation could possibly be resolved by one (or all) of the following actions:

a) Grouping IOBs of similar standards into a minimum amount of I/O Banks by using LOC or range constraints.

b) Maximizing available I/O Banks resources for special IOBs by choosing lower capacity I/O Banks if possible.

c) If applicable, decreasing the number of user prohibited sites or using a larger device.

Place:382 - The placer was unable to find a feasible solution for the IOBs in your design. This is possibly due to SelectIO banking constraints.

Each Group of a specific Standard is listed.

Standard SSTL18_II (Vref=0.90 Vcco=1.80 Terminate=none) 39 IOs, 39 locked.

(0-Inputs, 23-Outputs, 16-Bidirectional)

Standard LVCMOS25 (Vref=NR Vcco=2.50 Terminate=none) 9 IOs, 7 locked.

(1-Inputs, 7-Outputs, 1-Bidirectional)

Standard DIFF_SSTL18_II (Vref=NR Vcco=1.80 Terminate=none) 6 IOs, 6 locked.

(0-Inputs, 2-Outputs, 4-Bidirectional)

Standard LVCMOS18 (Vref=NR Vcco=NR Terminate=none) 3 IOs, 3 locked.

(3-Inputs, 0-Outputs, 0-Bidirectional)

Bank Summary

____________

If an IOB is placed in a dedicated Vref site, it will be indicated by the word 'Vref' at the end of a summ...

NOTE: This message is very long (~7 K) and has been shortened to a maximum of 1000 characters for viewing in this context.

Please refer to the corresponding ASCII report for the full message.

能帮帮我么?谢谢!卡了我好几天了。

你看一下你的引脚电平约束对了没 ? 所有的引脚都约束了吗?

你好,我是copy的开发板的顶层文件以及ucf,我认为是全都约束了。

NET "mcb3_dram_dq

NET "mcb3_dram_dqs" IN_TERM = UNTUNED_SPLIT_50;

NET "mcb3_dram_dqs_n" IN_TERM = UNTUNED_SPLIT_50;

NET "mcb3_dram_udqs" IN_TERM = UNTUNED_SPLIT_50;

NET "mcb3_dram_udqs_n" IN_TERM = UNTUNED_SPLIT_50;

############################################################################

# I/O STANDARDS

############################################################################

NET "mcb3_dram_dq

NET "mcb3_dram_a

NET "mcb3_dram_ba

NET "mcb3_dram_dqs" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_udqs" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_dqs_n" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_udqs_n" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_ck" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_ck_n" IOSTANDARD = DIFF_SSTL18_II;

NET "mcb3_dram_cke" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_ras_n" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_cas_n" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_we_n" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_odt" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_dm" IOSTANDARD = SSTL18_II;

NET "mcb3_dram_udm" IOSTANDARD = SSTL18_II;

#NET "c3_sys_clk_p" IOSTANDARD = LVDS_25;

#NET "c3_sys_clk_n" IOSTANDARD = LVDS_25;

NET "sys_clk_ibufg" IOSTANDARD = LVCMOS25;

NET "c3_sys_rst_n" IOSTANDARD = LVCMOS18;#LVCMOS18

############################################################################

# MCB 3

# Pin Location Constraints for Clock, Masks, Address, and Controls

############################################################################

NET "mcb3_dram_a[0]" LOC = "J7" ;

NET "mcb3_dram_a[10]" LOC = "F4" ;

NET "mcb3_dram_a[11]" LOC = "D3" ;

NET "mcb3_dram_a[12]" LOC = "G6" ;

NET "mcb3_dram_a[1]" LOC = "J6" ;

NET "mcb3_dram_a[2]" LOC = "H5" ;

NET "mcb3_dram_a[3]" LOC = "L7" ;

NET "mcb3_dram_a[4]" LOC = "F3" ;

NET "mcb3_dram_a[5]" LOC = "H4" ;

NET "mcb3_dram_a[6]" LOC = "H3" ;

NET "mcb3_dram_a[7]" LOC = "H6" ;

NET "mcb3_dram_a[8]" LOC = "D2" ;

NET "mcb3_dram_a[9]" LOC = "D1" ;

NET "mcb3_dram_ba[0]" LOC = "F2" ;

NET "mcb3_dram_ba[1]" LOC = "F1" ;

NET "mcb3_dram_ba[2]" LOC = "E1" ;

NET "mcb3_dram_cas_n" LOC = "K5" ;

NET "mcb3_dram_ck" LOC = "G3" ;

NET "mcb3_dram_ck_n" LOC = "G1" ;

NET "mcb3_dram_cke" LOC = "H7" ;

NET "mcb3_dram_dm" LOC = "K3" ;

NET "mcb3_dram_dq[0]" LOC = "L2" ;

NET "mcb3_dram_dq[10]" LOC = "N2" ;

NET "mcb3_dram_dq[11]" LOC = "N1" ;

NET "mcb3_dram_dq[12]" LOC = "T2" ;

NET "mcb3_dram_dq[13]" LOC = "T1" ;

NET "mcb3_dram_dq[14]" LOC = "U2" ;

NET "mcb3_dram_dq[15]" LOC = "U1" ;

NET "mcb3_dram_dq[1]" LOC = "L1" ;

NET "mcb3_dram_dq[2]" LOC = "K2" ;

NET "mcb3_dram_dq[3]" LOC = "K1" ;

NET "mcb3_dram_dq[4]" LOC = "H2" ;

NET "mcb3_dram_dq[5]" LOC = "H1" ;

NET "mcb3_dram_dq[6]" LOC = "J3" ;

NET "mcb3_dram_dq[7]" LOC = "J1" ;

NET "mcb3_dram_dq[8]" LOC = "M3" ;

NET "mcb3_dram_dq[9]" LOC = "M1" ;

NET "mcb3_dram_dqs" LOC = "L4" ;

NET "mcb3_dram_dqs_n" LOC = "L3" ;

NET "mcb3_dram_odt" LOC = "K6" ;

NET "mcb3_dram_ras_n" LOC = "L5" ;

#NET "c3_sys_clk_n" LOC = "K16" ;

#NET "c3_sys_clk_p" LOC = "K15" ;

NET "sys_clk_ibufg" LOC = "C9" ;#601_V10 V3_T8

NET "c3_sys_rst_n" LOC = "E4" ;#601_N4 ROCE_B16 V3_F8

NET "mcb3_dram_udm" LOC = "K4" ;

NET "mcb3_dram_udqs" LOC = "P2" ;

NET "mcb3_dram_udqs_n" LOC = "P1" ;

NET "mcb3_dram_we_n" LOC = "E3" ;

###################LED_DISPLY##################################

NET "led0" LOC = "A11" ;

NET "led1" LOC = "D9" ;

NET "led2" LOC = "E12" ;

NET "led3" LOC = "F9" ;

NET "led4" LOC = "F12" ;

NET "led5" LOC = "B11";

NET "load_data_i" LOC = "A13" ;

NET "load_data_ii" LOC = "C13" ;

NET "led0" IOSTANDARD = LVCMOS25;

NET "led1" IOSTANDARD = LVCMOS25;

NET "led2" IOSTANDARD = LVCMOS25;

NET "led3" IOSTANDARD = LVCMOS25;

NET "led4" IOSTANDARD = LVCMOS25;

NET "led5" IOSTANDARD = LVCMOS25;

NET "load_data_i" IOSTANDARD = LVCMOS18;

NET "load_data_ii" IOSTANDARD = LVCMOS18;

PIN "u_qd_ddr2_verilog/memc3_infrastructure_inst/U_BUFG_CLK0.O" CLOCK_DEDICATED_ROUTE = FALSE;