altera DDIO的时序分析讨论

时间:10-02

整理:3721RD

点击:

做DDR输入时序分析时,端口时序为clk 相对data delay2ns。蓝色时钟,黄色数据。时钟频率125M

timequest 分析得到

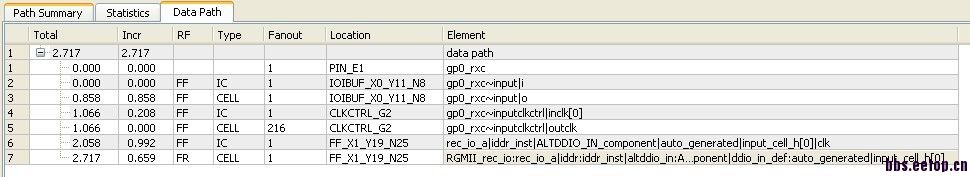

clk 到DDIO的寄存器clk端的延迟为下图

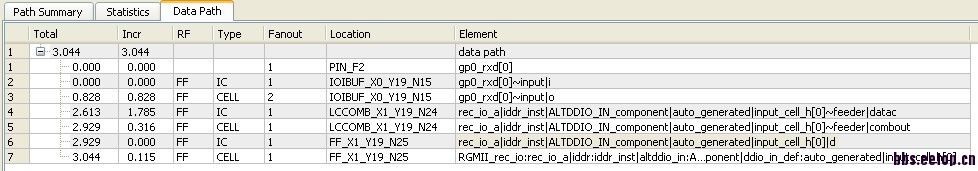

data 到DDIO的寄存器D端的延迟为下图

那么setup 欲量计算如下:2+2.058-2.929=1.129

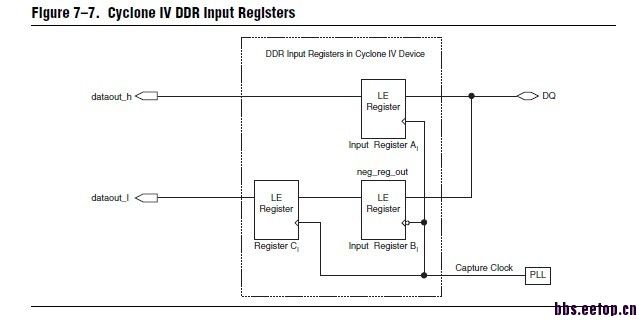

但是不明白timequest 上最后一项cell delay 指向input_cell_h的延迟是什么意思?难道是到寄存器Q端的延迟,但是这么理解的话CLK端怎么也会有这个延迟呢?谁知到最后一项延迟表示的意思?

查了datasheet 只有DDIO的块图

DDR的DQ是使用DQS去采样的

不是做DDR控制器的,是RGMII接口时序分析而已。

敢问小编DDIO的时序约束是怎么样的?