DC综合时BLACK BOX的pin脚约束!

时间:10-02

整理:3721RD

点击:

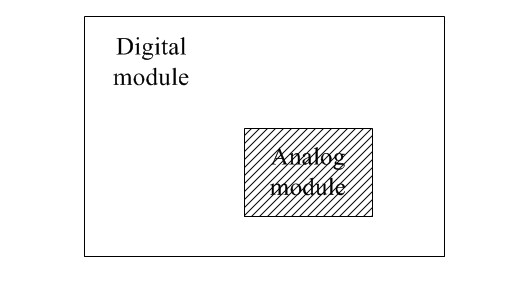

如上图,在一个系统中有数字部分和模块部分。在进行DC综合时,一般只考虑系统中的数字部分,而其模拟部分只是设置为一个空模块,即BLACK BOX.

如果是一些memory,则直接将.db例化进去却可;

但如果不是memory呢,其模拟模块出来的pin如何约束其时序,请高人指点,谢谢!

没有一个人回答?。

是不是可以通过set_input_delay和set_output_delay来设置!

帮忙顶一下,数模混合的东西不懂

数模混合之间涉及到信号和时钟的关系,如果是涉及到时钟的信号来源于模拟部分,你在写SDC时钟约束的时候要把时钟节点设置到模拟部分的pin上, 如果是涉及到信号的交互,你要确定模拟部分对信号的input(setup/hold),output(delay)时间是多少, 然后再SDC中用set_input_delay/set_out_delay 来约束信号和时钟之间的关系

谢谢回复,那你的回复与我的理解是一样的。 因为自己没有做过这样的综合,所以想问问有过此经验的大侠说下做法!

input_delay或者output_delay应该不是很合适吧? 个人觉得set_max_delay应该会合适一些。毕竟你关注的是输入/输出的delay。

混合信号数字模拟之间最主要的就是接口时序,接口时序的直接反映就是setup and hold time 检查,在set_input_delay and set_output_delay 你也可以加上max and min 参数去约束的。

顶贴赚积分