关于阻塞和非阻塞

哈哈,比如always结构语句,阻塞就是马上赋值,而非阻塞就是等到always结构结束后才赋值。

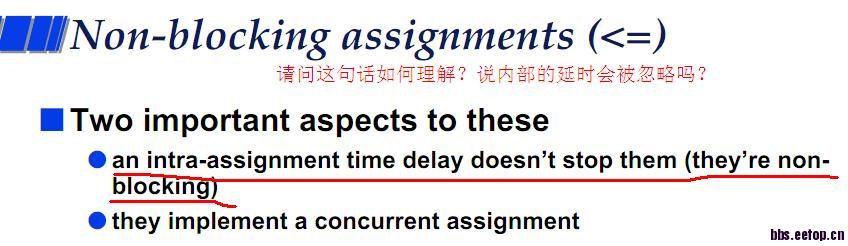

非阻塞赋值两个重要的方面:

1.语句内延时不能将非阻塞赋值语句挂起

2.非阻塞赋值语句实现了并行性赋值

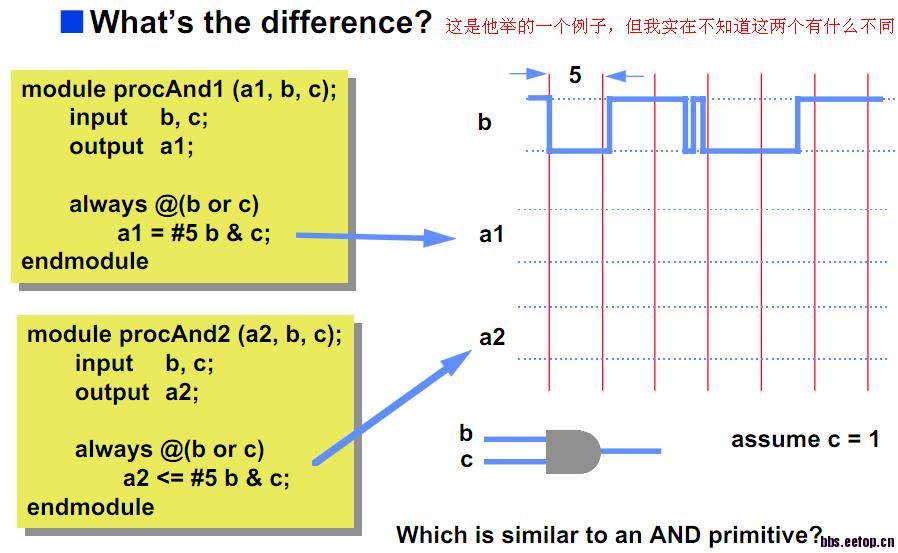

以下有何不同:

第一种语句不合法;

第二种语句合法,模拟了传播性延时

请问:

1 对于阻塞的语句,语句内的延时就起作用是吗?

2 既然对于非阻塞,延时不起作用,那为什么说“第二种语句合法,模拟了传播性延时”,然后第一种语句哪里不合法呢?

刚刚学Verilog,还请多多指教。

事件队列调度原因。

模块1,阻塞赋值,由于b改变,触发进程,先计算右式值,由于阻塞赋值会使该赋值表达式挂起,直到延时时间,才会将右式值赋给a1,所以在单位5延时时间内的任何b或c的改变都不能触发进程,将被忽略。这是不推荐的延时方式。

模块2,非阻塞赋值,同样由于b改变,触发进程,先计算右式值,由于非阻塞赋值不会使该赋值表达式挂起,仍然到延时时间会将右式值赋给a2,但在单位5延时时间内的任何b或c的改变仍然可以触发进程。所以该延时方式相当于任何发生的变化都在单位5延时之后赋值。模拟了类似于连线的延时,即传播延时。

说了那么多。有误的地方还请大家指出。

“=”用于组合逻辑,“<=”用于时序逻辑,

一般都是这么用的。用反了,sim tool应该会提示warning/error?

always@(b or c)

a = #5 b&c;

可以拆分成:

always@(b or c)

begin

d=b&c;

a=#5 d;

end

这样就清晰了,qjmxxgui 关于“事件队列调度原因”的解释还是很好的

哦哦,明白很多了!谢谢楼上的大虾!

这些东东我好像在书上都没有找到。都是要不停谷歌的。我现在看的是夏闻宇那本书,人人能都说好,但是我学起来却觉得很怪,就是觉得他都讲语法。但是我语法记起来了却理解不了,然后在写程序都不知道自己在写什么。而且书里仿真啊什么都完全不讲,学起来很郁闷。

夏宇闻的书确实不错,深入学习后会发现很有用。像你所说的阻塞赋值与费阻塞赋值,其实,你自己仿真一下,对比仿真结果就会明白它们的区别。刚开始学不一定要从语法学起,多做实例效果会更好

记住,你写的是硬件,而不是软件就行了。组合逻辑用阻塞赋值,不管你定义的是wire(assign语句)还是reg(always语句)类型,时序逻辑用非阻塞赋值(当然只能定义成reg,出现在always语句中),想到实现的是实际的电路就可以了。

zanyige

Joseph Cavanagh的《Verilog HDL数字设计与建模》后面有个附录是讲事件队列调度的,我觉得说的挺详细的。

将组合逻辑的always块的目标变量分成几个assign语句实现,你就立马明白了