求助以太网相关IP核例化

另外mdc,mdio_i的信号是哪里来的 谢谢了啊

看下ug476 36页 figure2-2 应该就是你说的那两个时钟 底层的gtx收发器

mdc和mdio用来配置phy寄存器的,它们是通过AXI产生的配置信息,你可以找一下代码。

不过现在的phy进本上默认最大速度全双工加自协商,所以这两个信号就不用管啦~

但是我并没有例化transceiver 的IP啊,这个时钟从还需要吗?

这两个信号还是需要的,因为我要读寄存器里的link_status的状态来判断sfp是不是link了,mdc和mdio我大概明白咋连了 谢谢啦

你看下这个IP的底层 都是例化的gtx 只不过在上层又包了不同的协议 比如srio pcie等。

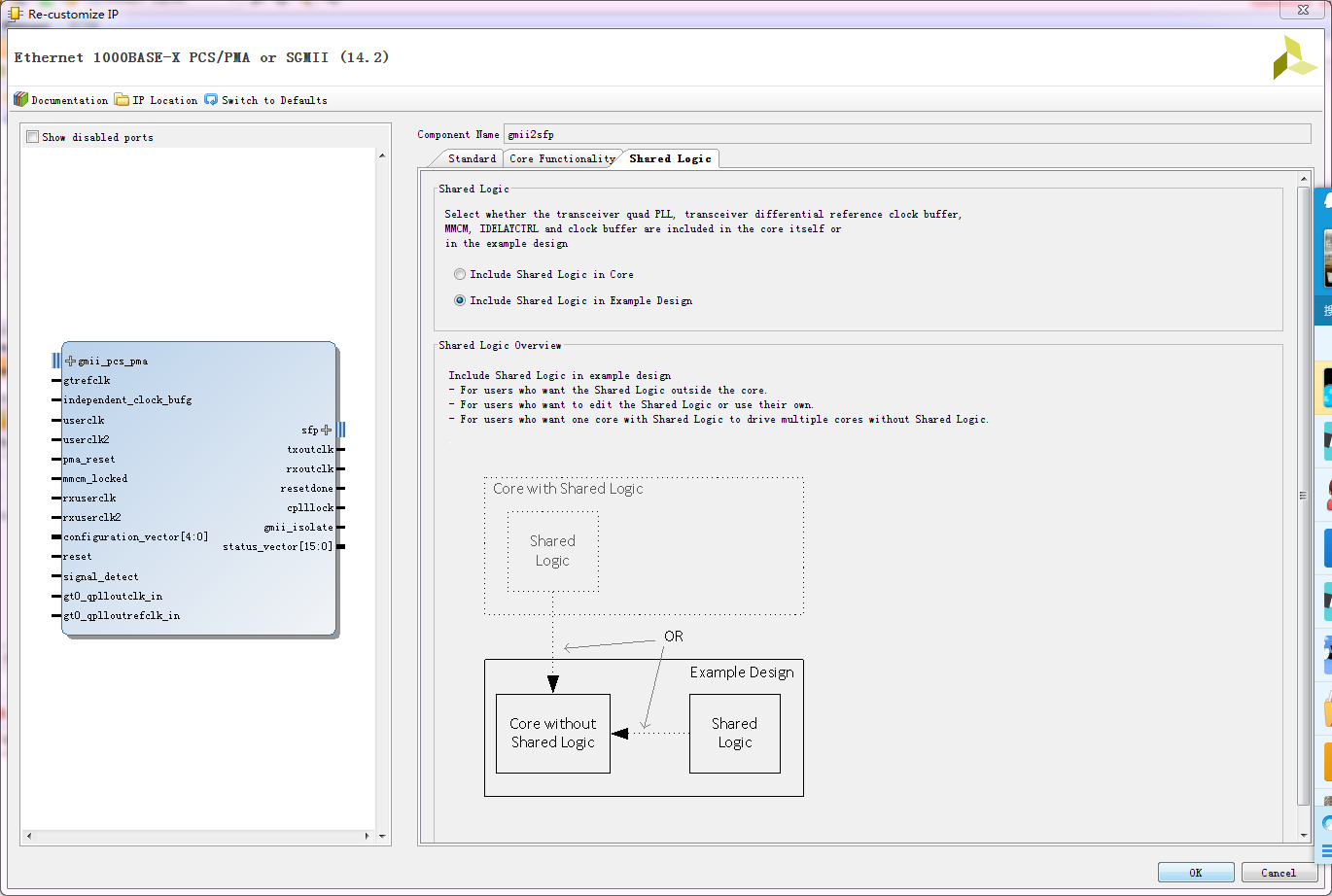

这样gtx应该是我Ethernet 1000base-x内部例化的,但是gt0_qplloutclk_in时钟和gt0_qplloutrefclk_in是我这个IP的外部接口:inst

(

// Transceiver Interface

//----------------------

.gtrefclk (gtrefclk),

.txp (txp),

.txn (txn),

.rxp (rxp),

.rxn (rxn),

.resetdone (resetdone),

.cplllock (cplllock),

.txoutclk (txoutclk),

.rxoutclk (rxoutclk),

.userclk (userclk),

.userclk2 (userclk2),

.rxuserclk (rxuserclk),

.rxuserclk2 (rxuserclk2),

.independent_clock_bufg (independent_clock_bufg),

.pma_reset (pma_reset),

.mmcm_locked (mmcm_locked),

// GMII Interface

//---------------

.gmii_txd (gmii_txd),

.gmii_tx_en (gmii_tx_en),

.gmii_tx_er (gmii_tx_er),

.gmii_rxd (gmii_rxd),

.gmii_rx_dv (gmii_rx_dv),

.gmii_rx_er (gmii_rx_er),

.gmii_isolate (gmii_isolate),

// Management: MDIO Interface

//---------------------------

.mdc (mdc),

.mdio_i (mdio_i),

.mdio_o (mdio_o),

.mdio_t (mdio_t),

.configuration_vector (configuration_vector),

.configuration_valid (configuration_valid),

// General IO's

//-------------

.status_vector (status_vector),

.reset (reset),

.signal_detect (signal_detect),

.gt0_qplloutclk_in (gt0_qplloutclk_in),

.gt0_qplloutrefclk_in (gt0_qplloutrefclk_in)

);

就像是这样,我就不清楚最后两个改连哪里了

刚才生成了一个你说的IP看了下 并没有你说的这两个时钟啊 你用的IP是不是被修改过 把这两个时钟引出来了。 看名字这两个时钟应该是QPLL的参考时钟和PLL的输出时钟 都是GTX的输出 ,如果不需要悬空不可以吗?

我基本都没改 我还是选择的最简单的模式,MDIO,auto negotiation我都没加,我看不管哪种都有这个两个时钟; 我就是不清楚如何处理这两个时钟,我就直接给连了一个125MHz,现在还在调试 还不知道这样行不行

你用的是vivado的哪个版本啊 版本不一样IP核确实差别挺大的

14.1的 coregen生成的 核的版本是2.2

我是2014.2版本的,应该差不多才对的,但是咋样都会有那两个时钟

我是2014.2版本的,应该差不多才对的,但是咋样都会有那两个时钟

vivado的和coregen接口确实不太一样 可能你的版本更高