FIFO写时碰到的问题

parameter T1S = 32'd49_999_999;

reg [47:0] Data_out = 48'b00010001_00100010_00110011_01000100_01010101_01100110; //11 22 33 44 55 66;

always @ (posedge clk_a or negedge rst_n)

if(!rst_n)

cnt_1s <= 25'd0;

else if (cnt_1s == T1S)

cnt_1s <= 25'd0;

else

cnt_1s <= cnt_1s +1'b1;

assign wr_req =(cnt_1s >= 32'd49_999_994)&&(cnt_1s <= 32'd49_999_999);

always @ (posedge clk_a or negedge rst_n)

if(!rst_n)

wr_datain_r <= 8'd0;

else if((cnt_1s >= 32'd49_999_994)&&(cnt_1s <= 32'd49_999_999))

begin

timer1s <= 1;

case (i)

0: begin wr_datain_r <= Data_out [ 7:0]; i <= i+1; end

1: begin wr_datain_r <= Data_out [15:8]; i <= i+1; end

2: begin wr_datain_r <= Data_out [23:16]; i <= i+1; end

3: begin wr_datain_r <= Data_out [31:24]; i <= i+1; end

4: begin wr_datain_r <= Data_out [39:32]; i <= i+1; end

5: begin wr_datain_r <= Data_out [47:40]; i <= 0; end

endcase

end

else

begin

timer1s <= 0;

wr_datain_r <= 8'd0;

end

assign wr_datain = wr_datain_r;

这个程序非常简单,不过

1,FIFO并没有读;

2,你的问题应该是FIFO写出错;

3,没有看到i的定义;

至于为什么取数为什么出错,在线看一下i的值,一步一步找问题呗;

另外,你写数的时序明显没有对齐。

我这个只是截取了写的部分程序,读的部分没贴出来,因为通过串口输出,直接从串口助手就可以看到输出了,跟那个wr_datain的数值是一样的,

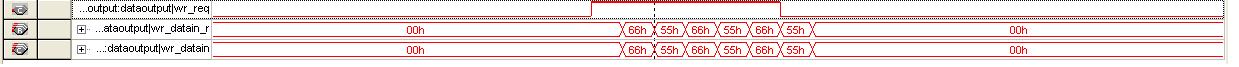

另外那个i的定义可能有问题,我现在定义成reg [2:0] i. 可是程序现在写却变为00 66 55 55 55 55;出现这个00应该是你所说的时序没有对齐导致,

请问,如何对齐时序?另外那个i的定义,包括case语句里该如何修改?如您所说,简单的问题,可是已经被卡了快一周了,麻烦了!

把i的值0,1,2,3,4,5,换成“000”,“001”,“010”,“011”,“100”,“101”试试;其实我也不能确定问题在哪里;

你不能看一下i的值吗?

时序对齐的话,可能方法比较多,

可以把wreq延时一个时钟,即在clk下打一拍送至fifo。

我看了下i值,程序的变化是0h,1 h, 2h,其中2h占据了4个时钟,然后又变为0h。

我把wr_req延迟一个时钟,然后现在时序能对得上了,可是接收到的数据是66 55 55 55 55 55.相应的i值是1h, 2h,2h, 2h, 2h, 2h,

有些奇怪的问题肯定是有缘由的,一步一步认真找;

或者你可以改用状态机;

或者用其他方法,多试一下。

i 没给初值吧。在reset中赋0.试试

i的初始值没有看见在哪里?i的宽度对吗?

你确定你的程序是完整的?仿真过?

把rtl描述称为程序。

不知道rtl描述的是什么电路。

不改的话,以后基本上很难了。

最近在研究SRAM读写问题,存入SRAM之前也需要FIFO进行数据缓存,能否加个好友共同学习。

cnt_1s 25 比特 好像也不够啊

你这个程序可读性太差了,看了之后就没有去分析的欲望。