Verilog代码问题

时间:10-02

整理:3721RD

点击:

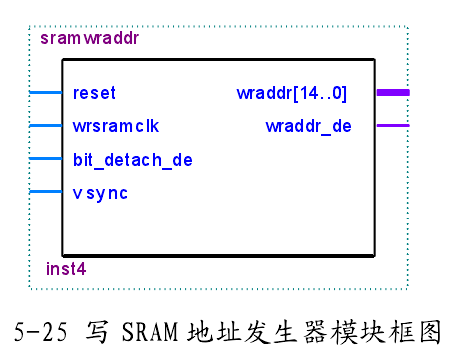

- [code]module sram_wraddr(

input sram_wrclk,

input rst_n,

input cmos_vsync,

input bit_detach_de,

output reg[14:0] sram_wraddr,

output reg[1:0] sram_wraddr_de

);

parameter [3:0]

START=0, //开始状态

IDLE=1, //复位状态

WAIT_NEWD=2, //等待新的数据状态

NEW_DATA=3, //新的数据到来状态

SRAM_WR=4 ;

//写SRAM状态

reg [14:0] wraddr_count; //写SRA计数器,后面将计数器的值赋给SRAM地址

reg [1:0] current_state,next_state;

//---------- sram_write second course----------- SRAM写过程第一进程

always@(posedge sram_wrclk or negedge rst_n)

begin

if(!rst_n)

begin

current_state<=START;

end

else

begin

current_state<=next_state;

end

end

//---------- sram_write second course----------- SRAM写过程第二进程

always@(*)begin

next_state=START;

case(current_state)

START: begin

if(!rst_n)

next_state=IDLE;

else

next_state=START;

end

IDLE: begin

if(cmos_vsync==0)

next_state=WAIT_NEWD;

else

next_state=IDLE;

end

WAIT_NEWD: begin

if(cmos_vsync==1)

next_state=NEW_DATA;

else

next_state=WAIT_NEWD;

end

NEW_DATA: begin

if(bit_detach_de==1)

next_state=SRAM_WR;

else

next_state=NEW_DATA;

end

SRAM_WR: begin

if(wraddr_count==30720)

next_state=NEW_DATA;

else

next_state=WAIT_NEWD;

end

default: begin

next_state=IDLE;

end

endcase

end

//--------------sram_write third course--------------- SRAM写过程第二进程

always@(posedge sram_wrclk or negedge rst_n)

begin

if(!rst_n)

begin

wraddr_count<=0;

sram_wraddr_de<=0;

sram_wraddr<=0;

end

else if(current_state==SRAM_WR)

begin

if(wraddr_count==30720)

begin

wraddr_count<=0;

sram_wraddr_de<=0;

end

else

begin

wraddr_count<=wraddr_count+1;

sram_wraddr_de<=1;

sram_wraddr<=wraddr_count;

end

end

end

endmodule

[/code]

测试testbench文件

- module sram_wraddr_tb;

- // Inputs

- reg sram_wrclk;

- reg rst_n;

- reg cmos_vsync;

- reg bit_detach_de;

- // Outputs

- wire [14:0] sram_wraddr;

- wire sram_wraddr_de;

- // Instantiate the Unit Under Test (UUT)

- sram_wraddr uut (

- .sram_wrclk(sram_wrclk),

- .rst_n(rst_n),

- .cmos_vsync(cmos_vsync),

- .bit_detach_de(bit_detach_de),

- .sram_wraddr(sram_wraddr),

- .sram_wraddr_de(sram_wraddr_de)

- );

- parameter CYCLE= 20;

- parameter RST_TIME= 3;

- initial begin

- sram_wrclk = 0;

- forever

- #(CYCLE/2)

- sram_wrclk=~sram_wrclk;

- end

- initial begin

- rst_n=0;

- #(CYCLE*RST_TIME)

- rst_n=1;

- end

- initial begin

- cmos_vsync=0;

- bit_detach_de=0;

- #(5*CYCLE)

- cmos_vsync = 1;

- bit_detach_de = 1;

- end

-

- endmodule

测试出波形不对,输出的地址计数器一直为0,没有变化。

请大家帮忙看下,我写的这个代码,或是测试代码出现什么问题,刚开始写代码没多久,希望大家多多指点。

SRAM_WR的跳出状态的控制有问题。按上面写法进入SRAM_WR状态下一个cycle就跳出这个状态了。

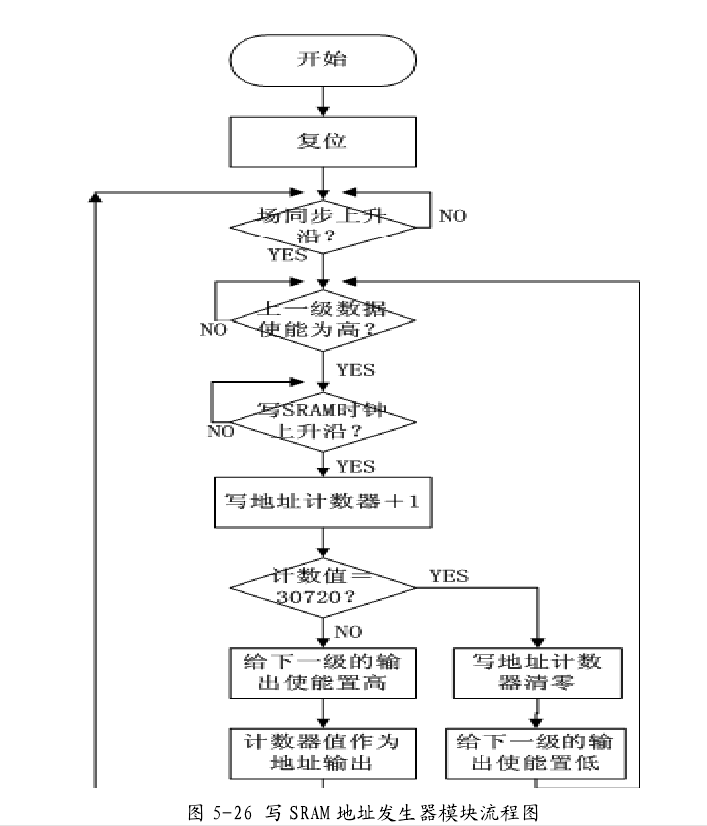

我给发下流程图,你能帮我看下吗?

你这个流程似乎没问题,但是你这个代码写得和你的图不一样。原因就是2L说的那样

而且他这个代码好像时序还有问题,建立时间和保持时间做过分析吗

你可以参考下面链接中我写的双端口读写的代码

http://bbs.eetop.cn/viewthread.p ... p;extra=&page=5

没有,完全新手,还有好多要学习,望大家多多指点

建立时间和保持时间,还没分析,现在只想先试试这段程序能不能跑通,还有好多工作要弄。

START: begin

// if(!rst_n) 这些都没用

next_state=IDLE;

// else

// next_state=START;

end