Dc综合各种warning截图,求助

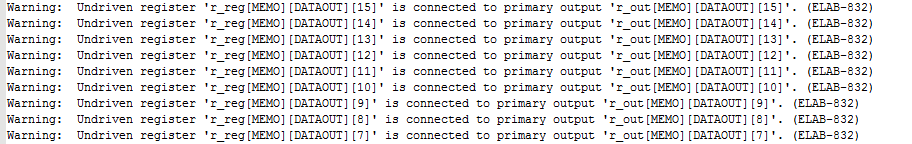

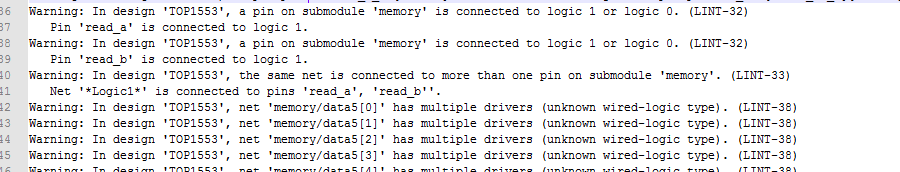

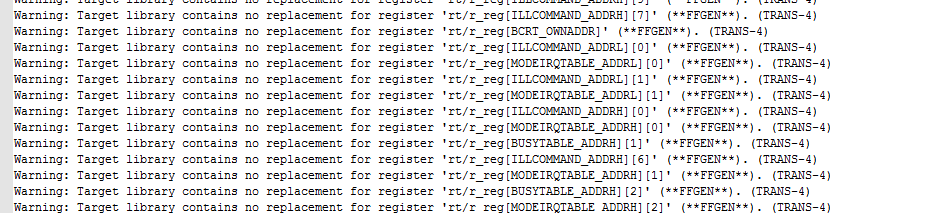

第一种:

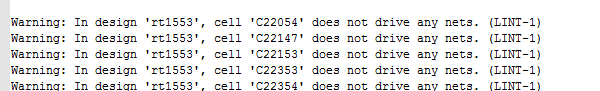

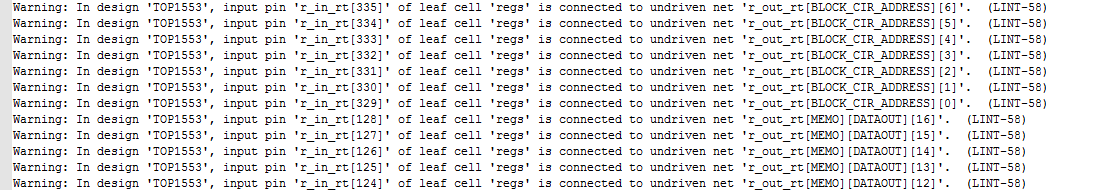

第二:

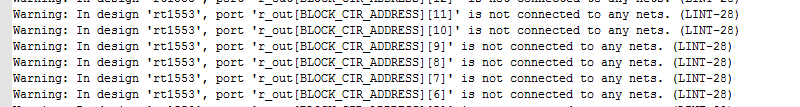

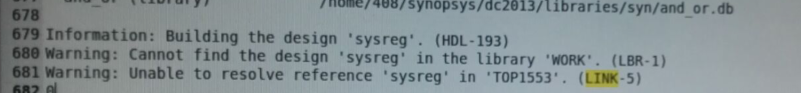

第十。

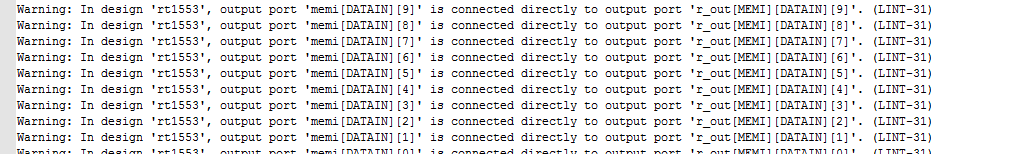

简直各种警告的大全集。每种都有好几十,最多的一百多,不知道是哪个导致后仿的x态的

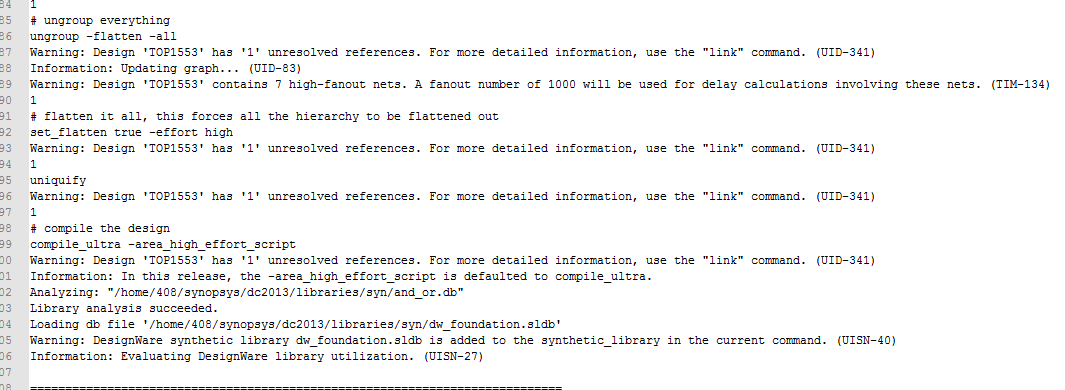

DC的warning不是需要全部清掉的,你的第一第二种显然不用管。第八种,报错了,必须清掉,有unresolved references,查看你的link报告。link报告为“1”是DC正确的最基本条件。

大神。什么是link报告啊。

你先把第八种错误清掉再说,查看log文件也可以。在读进RTL设计后,link步骤生成的report必须正确。

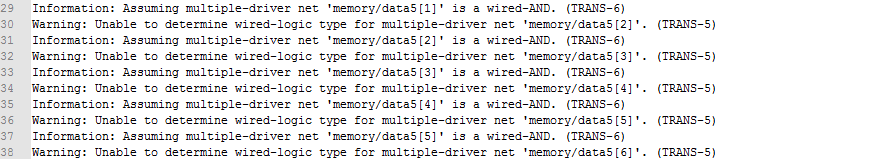

muti-driven lint-38 必须fix. 有这种问题,DC 应该直接退出!而且你这个FM肯定fail.

大神,恳请详细批示!因为我确实不懂。 dc综合好像过了。出来网表了,也不知道咋回事。

现在是后仿有x态

并不是说DC综合出网表了就意味着DC的结果是正确的啊,你还要去看DC的report确认有没有问题,以及楼上说的,formality保证。

大神,log里面没报错啊。我也很急切想解决这个警告,现在我不知道这个

Design 'TOP1553' has '1' unresolved references. For more detailed information, use the "link" command. (UID-34

到底是咋回事,Link命令我都不会用啊。,对了.synopsys.setup里面设置了link库,不知道脚本里面怎么用link命令。

求助大神啊。link命令加到哪一行?什么形式

#@ #####################################

#@ # Current Design: TOP1553

#@

#@ # Load up design files

#@ # uncomment one of the following

#@ #analyze -format verilog TOP1553.v

#@ analyze -format vhdl {if1553.vhd sysreg.vhd fifo.vhd transmitter.vhd rt1553.vhd receiver.vhd encode10m.vhd encode.vhd dpram.vhd decode10m.vhd decode.vhd TOP1553.vhd}

#@

#@ # Tell dc_shell the name of the top level module

#@ elaborate TOP1553

#@

#@ # set a clock

#@ create_clock {ext_clk clk}

#@

#@

#@ # Check for warnings/errors

#@ check_design -multiple_designs

#@

#@ # ungroup everything

#@ ungroup -flatten -all

#@

#@

#@

#@ # flatten it all, this forces all the hierarchy to be flattened out

#@ set_flatten true -effort high

#@ uniquify

#@

#@ # compile the design

#@ compile_ultra -area_high_effort_script

#@ #compile_ultra -timing_high_effort_script

#@ #compile_ultra

#@

#@

#@

#@ # Now that the compile is complete report on the results

#@ report_area

#@ report_timing

#@ report_power

#@

#@

#@ write_sdf top1553delay.sdf

#@ ############################### begin: renaming section

#@ # remove the following renaming section when not needed

#@ # define the name rules for rename

#@ define_name_rules verilog -remove_port_bus

#@ define_name_rules verilog -remove_internal_net_bus

#@

#@ # name rule for nets

#@ define_name_rules verilog -type net -allowed "a-z A-Z 0-9 " -first_restricted "0-9 N" #-replacement_char "_" -prefix "n"

#@

#@ # name rule for cells

#@ define_name_rules verilog -type cell -allowed "a-z A-Z 0-9 " -first_restricted "0-9" #-replacement_char "_" -prefix "u"

#@

#@ # name rule for ports

#@ define_name_rules verilog -type port -allowed "a-z A-Z 0-9 " -first_restricted "0-9" #-replacement_char "_" -prefix "p"

#@

#@ # change names of variables

#@ change_names -rule verilog -hierarchy

#@

#@ ################################ end: renaming section

#@

#@ # Write out the design

#@ write -f verilog TOP1553 -output TOP1553_syn.v

#@

#@ remove_design -all

#@

#@ exit

elaborate TOP1553后加link

Design 'TOP1553' has '1' unresolved references,这个必须清掉,你是不是有一个模块文件没有添加到你vhdl的文件列表里?

大神,link用了,详细报出来了warning:

可是我脚本明明加了它啊。还有top层和这个模块的映射也正确。怎么就找不到呢?

居然是这么大的问题!居然就给个warning....我理解应该是error了。谢谢大神高招。弱问一下。如果映射没错,可能是什么原因导致找不到这个模块?

unresolved references 在DC里面确实只是Warning不是Error,所以一定要先保证link没有问题,DC才有必要往下走。不过现在问题已经很明确且范围缩小到sysreg上了,只能靠你自己去检查设计或者是哪里的设置问题了。

这个warning解决了。现在还是后仿不过。最后在厚脸皮请教一次。大神给我指出一下几个必须要消灭的warning吧。就是你们的经验

对了。现在出来了个新的warning:

Warning: Design 'TOP1553' contains 8 high-fanout nets. A fanout number of 1000 will be used for delay calculations involving these nets. (TIM-134)

因为要全消灭,工作量太大了。哎。你也看到了我那几百warning

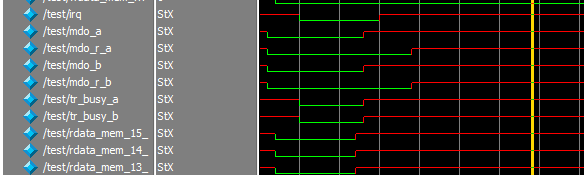

对了。dpram模块。因为需要实现双出双入双时钟。我用了shared variable会不会导致不可综合?下图是我后仿的顶层输出端口,在前仿时,配置完寄存器,mdo_b,和mdo_r_b都是正常输出,现在是配置完寄存器后一段时间(绿线段),就红了。就红了!这个折磨我很久了。

1、是否存在不可综合的,你要去看DC的报告,另外DC后的网表和RTL的formality比对也可以检查

2、即使正确的DC网表,仿真跑红也不奇怪的,因为DC没有时钟树,hold的violation是没清的。一定要拿DC的网表仿真,只能手工去修改sdf以满足时序,这个就看你们自己了。

膜拜!谢谢啊。我开始手工改sdf....我们这很奇葩,综合出来网表格式是data_1_,sdf是一个炉子出来的格式却是data_reg[1]。

我都对此放弃了,原来还是要带sdf啊。我今天试试手工改动之!

谢谢大神!你真好心!祝你健康愉快啊!