对DDR3读写不稳定,KC705开发板

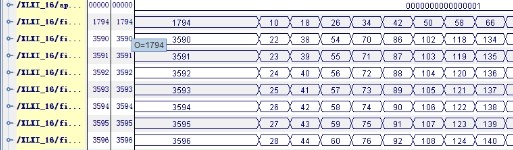

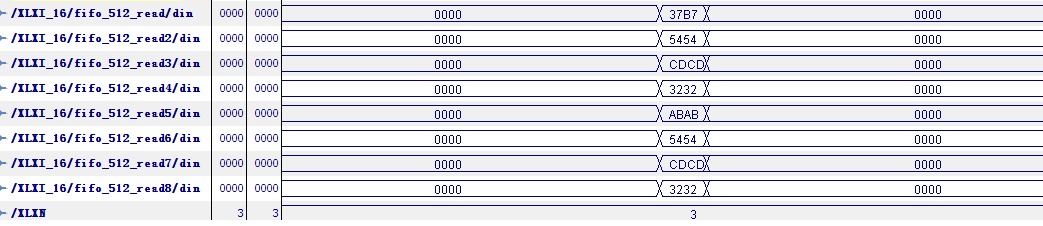

但是有少数时候,读出数据为0,如下图:

相同的bit文件,第一次调DDR,有明白的指点下。

有一点没说太明白,如果上电配置完成后首次读出正确,则以后读出数据一直正确;如果上电配置完成后首次读出数据错误,则一直错误。

谢谢,初始化肯定是完成了的,读写操作都是在初始化完成后开始的。所有操作都一样,就是有时候结果不一样。还有什么别的初始化吗?自己再顶一下,好有人来回答

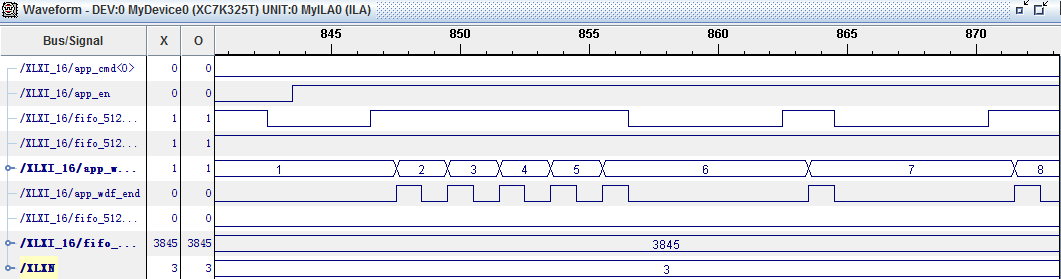

继续往前移啊,有人遇到这种情况吗,我把时钟约束稍微设高了点,从200加到205M,还是有这问题,chipscop抓的读数据,有时读对,有时候错,抓的写操作都一样啊。求解啊

看看是不是对DDR颗粒的初始化没弄对

怎么看初始化对不对啊,我用的核,谢谢啊上传一个写操作的图,不管读出数据是对是错,写操作都是一样的

第三行是app_rdy,第四行是app_wdf_rdy,一直高电平,最下面是init_calib_complete,一直为高电平

结贴了,调差不多了。希望能对别人有点借鉴意义。我只能说调试别人是帮不了你的,逛逛论坛,启发一下倒是真的,一百个人调试,一百个不同的问题,让人怎么帮。

原因找到了没有呀?

找到了,主要是不能马上对写地址进行读操作时序是没有问题的么?时钟连接完全与文档一致吗?

您好!如果初始化过程长时间都完成不了,也就是仿真很久之后init_calib_compelte信号一直为低电平,会是哪些原因引起的呢?有没有解决的办法?

颗粒参数配置对不对用过 AC701 KC705 内存DDR3测试都是比较简单,按照参考,很容易测试。 自己搞一个状态机仿佛读写,未出现异常。 只要calib_done 完成了,读写每次都正确。只是读的时候要等待十几个时钟周期。 联系测试12个小时反复读写,未出现任何错误. (AC701/KC705板测试)

你好,我调试DDR3也遇到类似的问题,读写时序和数据手册上的都是一样的,但读出来的数据顺序是乱的,比如我往连接的地址里写入1到1000,但读出来的数据是从950开始到1000,然后才是1到949,有时候又是对的,我写操作完成后,间隔了2000个时钟周期,还会是什么问题呢,求指点。

请问我为什么一直初始化失败啊,与其说失败,还不如说根本什么都有做,就是建立ip核,然后写读写程序,想先跑一跑仿真,然后一点一点来。可是第一步就是大难题啊。不给初始化,app_rdy信号也不给调高。不知从何入手。你好,我用Cyclone V ,例化DDR3的时候,在300MHz时可以读写DDR3,400MHz时,读写失败,这个有谁遇到过么,大概是什么原因?谢谢了,有谁知道的帮小弟个忙