后仿真延时问题

时间:10-02

整理:3721RD

点击:

各位大虾:

我在读入SDF文件进行后仿真的时候,发现仿真的波形里面寄存器的延时还是标准延时, 当然仿真是没有通过的,也就是说 “标准单元里面的specify 时间没有被SDF的参数所从新定义”,netlist 和SDF是相符合的,但是读取SDF的时候有一个Warring: Read error for default code, 哪位大虾知道这是什么问题? 急求解答

我在读入SDF文件进行后仿真的时候,发现仿真的波形里面寄存器的延时还是标准延时, 当然仿真是没有通过的,也就是说 “标准单元里面的specify 时间没有被SDF的参数所从新定义”,netlist 和SDF是相符合的,但是读取SDF的时候有一个Warring: Read error for default code, 哪位大虾知道这是什么问题? 急求解答

帮顶了

问题已经解决了

出来说明一下呗!

有可能是工具版本的问题, 我先前是后仿真都通过的,也就是说SDF反标是成功的,但是自己做布局布线感觉不理想,就从新布局布线, 就发现后仿不对了。 原本以为是网表和SDF不不匹配,但是查看结果是匹配的。查看PT生成的SDF文件, 里面有参数, 应该是反标上去了的。 但是后仿编译的时候报告的时候报告一个Warring,后面再PT脚本里面生成SDF的命令 wirte_sdf 后面加上参数就可以了,网上搜索的帖子 -context verilog -input_port_nets -output_port_nets -no_edge, 但是我也很纳闷的是, 我先前又能反标上去, 只是从新做了布局布线而已

还是不太明白

虽然上面的问题解决了 , 从那以后我没有用过ncvlog, 两个不同工具厂商之间的兼容性不同, 我现在仿真工具就用vcs , 做了这么多的项目,PT 出来的sdf vcs 读入还有什么问题的

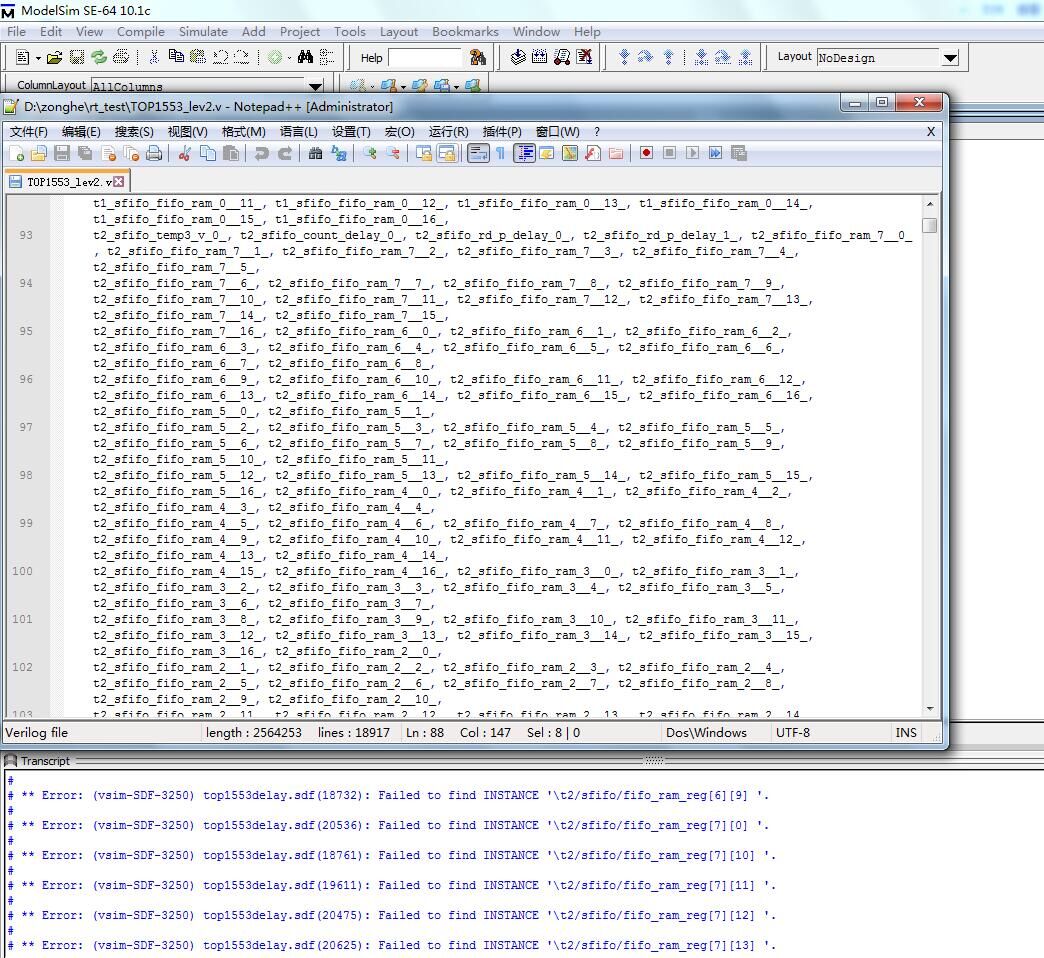

大神能不能指点一下反标?我是遇到了sdf和网表不匹配。麻烦看看