使用$readmemh命令编写Verilog测试模块循环读取时遇到问题,请大神帮助

时间:10-02

整理:3721RD

点击:

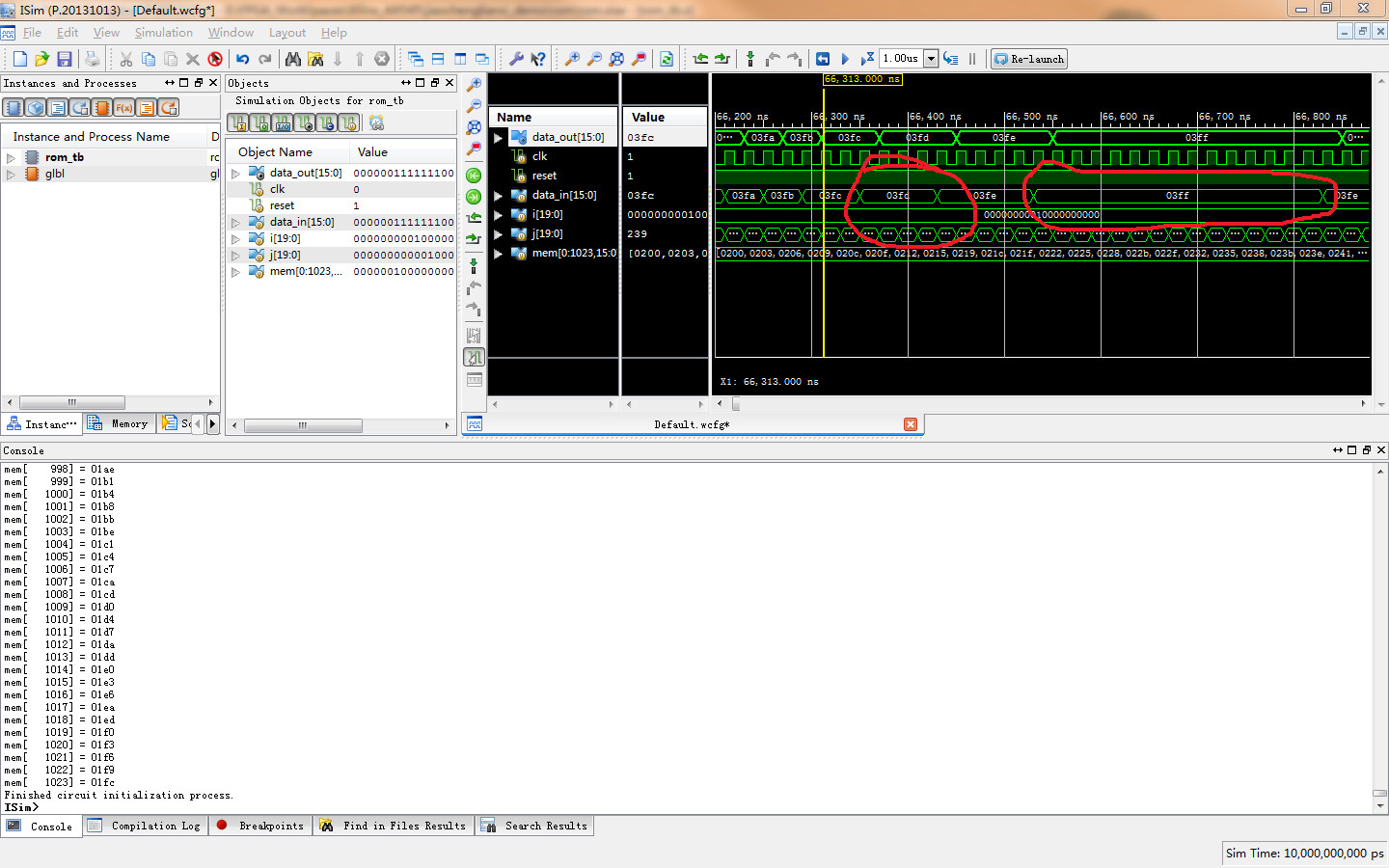

先使用MATLAB生成了16位宽度,1024深度的正弦波数表,想使用$readmemh命令编写Verilog测试模块产生正弦激励波形,仿真表明初始化成功,但循环读取时错误,读到的数据不变且不正确。图1仿真结果。

data_in[j] <= mem[j]; 改为 data_in <= mem[j];

还是大神厉害!

改过来之后又出现了另一个问题:读数周期大部分时候是一个周期,有时会出现两个甚至多个周期,如图所示,何解?

是不是此时mem[j]的数据就是一样的,比如mem[219]=mem[220]=mem[221].

我知道了,这是正常的现象,因为数表中的这几个数就一样,感谢回答!