xilinx MIG进行modelsim后仿真时候出现的问题。

Module parameter 'ADDITIVE_LAT' not found for override.

# Region: /sim_tb_top

Error: (vsim-3584) D:/first/mig_test4xst/ncsim/rtl/sim_tb_top.v(347): Module parameter 'APPDATA_WIDTH' not found for override.

# Region: /sim_tb_top

# ** Error: (vsim-3584) D:/first/mig_test4xst/ncsim/rtl/sim_tb_top.v(347): Module parameter 'BANK_WIDTH' not found for override.

# Region: /sim_tb_top

# ** Error: (vsim-3584) D:/first/mig_test4xst/ncsim/rtl/sim_tb_top.v(347): Module parameter 'BURST_LEN' not found for override.

(vsim-3584) D:/first/mig_test4xst/ncsim/rtl/sim_tb_top.v(347): Module parameter 'CKE_WIDTH' not found for override.

这个是我的SDF路径没有指定正确呢还是本身sdf就错了

都报的是参数的错误啊。你这几个参数在调用的时候传进去了吗?

你是在FPGA里面用这个MIG吗? 如果是,那其实真可以不用后仿的。前仿过了就直接上板子上测吧。DDR的问题要上班才看得出来,比如DQS, DQ走线有没有问题,都要上板才能发现的。

是的,我用ISE13.1生成IP核,然后极性后仿真的。 怎么传进去呢?通过网表是嘛?我跑的频率才125M,但是不做后仿真下板子有点担心了,后仿真也是各种出错

FPGA接口的东西很少后仿的,因为后仿cover不到片外情况,意义不大。做完前仿真之后,做个小的测试工程直接上板子验证才有意义。

这些参数你在SIM_TB_TOP调用的时候要赋值的,在generic里面赋值,如果是verilog就是parameter。

你这个CORE是什么情况啊,burst length是多少?数据线dq位宽是多少啊?bank还有cke,这些位宽都是多少啊?如果sim_tb_top是你的顶层,那你应该是要把这些参数定义成local param,然后传进去的。

你是不是直接用的mig生成的testbench做的后仿?

回复 4# catcat_2

非常谢谢你的即使回答,真的很感谢。

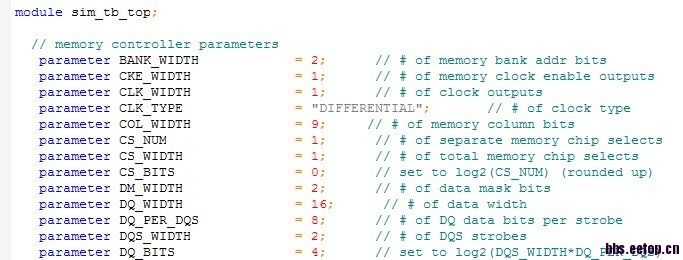

我是直接用的mig生成的testbench做的后仿,直接SIM_TB_TOP作为上层tb文件的,没有做任何的修改。难道这个tb不对吗,我看到在tb里边所有的参数都是以paremeter进行赋值了,进图片。

我的core是用ISE13.1也就是MIG3.6,我直接用core生成的文件还有sim.do仿真的,其中burst length=4,dq=16,bank=2.cke=1,这些在SIM_TB_TOP中直接就是paremeter,不是local paremeter.

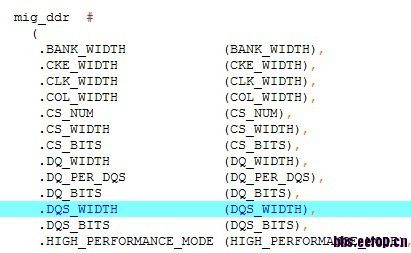

但是我前仿的时候没遇到这个问题,是后仿加入SDF,mig_ddr_timesim.v才报错的

你好,请问你是用的V5哪个系列呢?能不能给个联系方式?有问题请教?

你的片外应该就只有一个DDR2 SDRAM,位宽是8bit,然后你的BL=4,那么UI上面就是32bit。

这个没有问题。如果你实在想做后仿的话,你尝试下直接把那几个报错的参数写死,你自己应该会算吧。

不过,前仿都过了,还是直接上板看吧,后面问题保不准还有呢。不要在后仿这费时间了。反正是FPGA,不是ASIC。

记得把那个跳过initialise的参数改回来。chipscope上面把phy_init_done那个信号加进去,有没有什么ocb_monitor啊,记得OFF掉。然后把phy层有一个初始化的状态机加进去,如果init_done没过,这个是需要查的。

找您这个帖子好辛苦呀,我最近才开始学习这个XILINX MIG,请问怎么做仿真呢,具体步骤是什么呀,希望您一定要看见我的问题,给我回复指导呀,谢谢。

对了,还有这位大侠,希望您能回复我,这个生成的MIG,怎么做modelsim仿真呢?跪求了!

example_design\sim中有个sim.do

直接进入此目当,在modelsim中 do sim.do执行就可以了。

您好,我做了mig的前仿,输出的数据和app_addr没有问题,但是上板就有问题了。phy_init_done信号可以拉高,但是地址比较混乱,所以想做一下后仿,在modelsim中遇到了与您同样的问题,请问您是怎么解决的?