Xilinx DDS Compiler IP核使用问题,用过的高手来看一下

时间:10-02

整理:3721RD

点击:

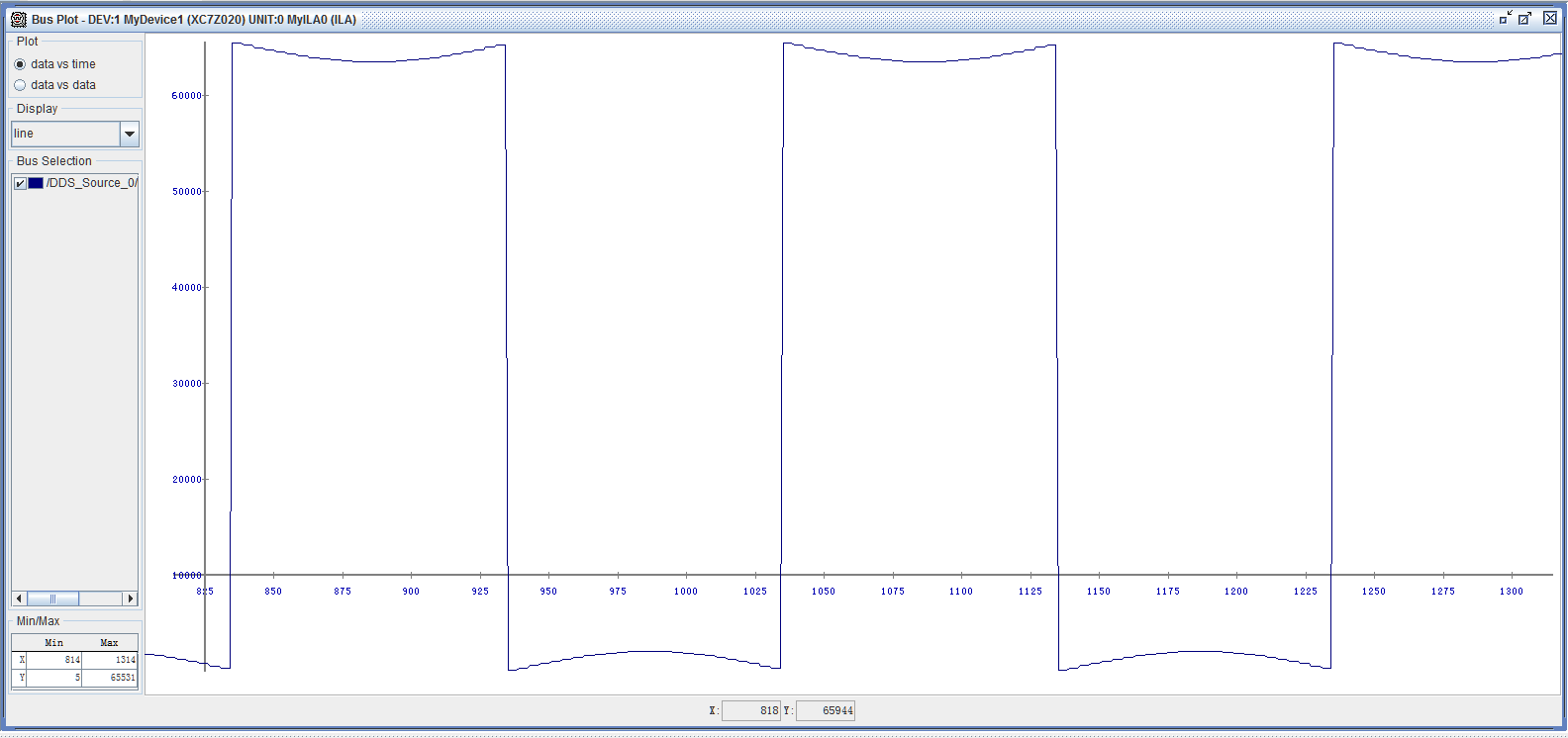

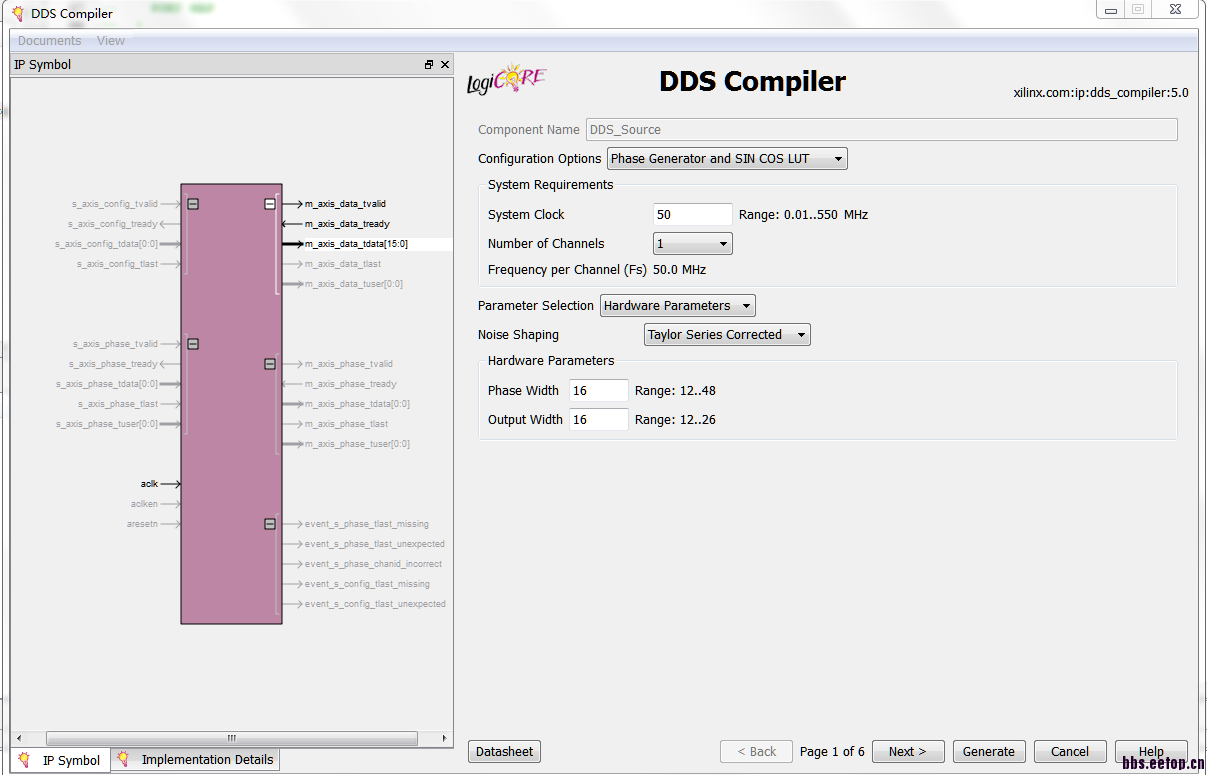

我要在FPGA中做数字正交,故此要用到DDS IP核,但是研究了两天始终无法产生比较满意的正玄波,用ChipScope采到的波形要不是就是像下图这种,要不就是一些比较混乱的,反正不是比较正常的正玄波。

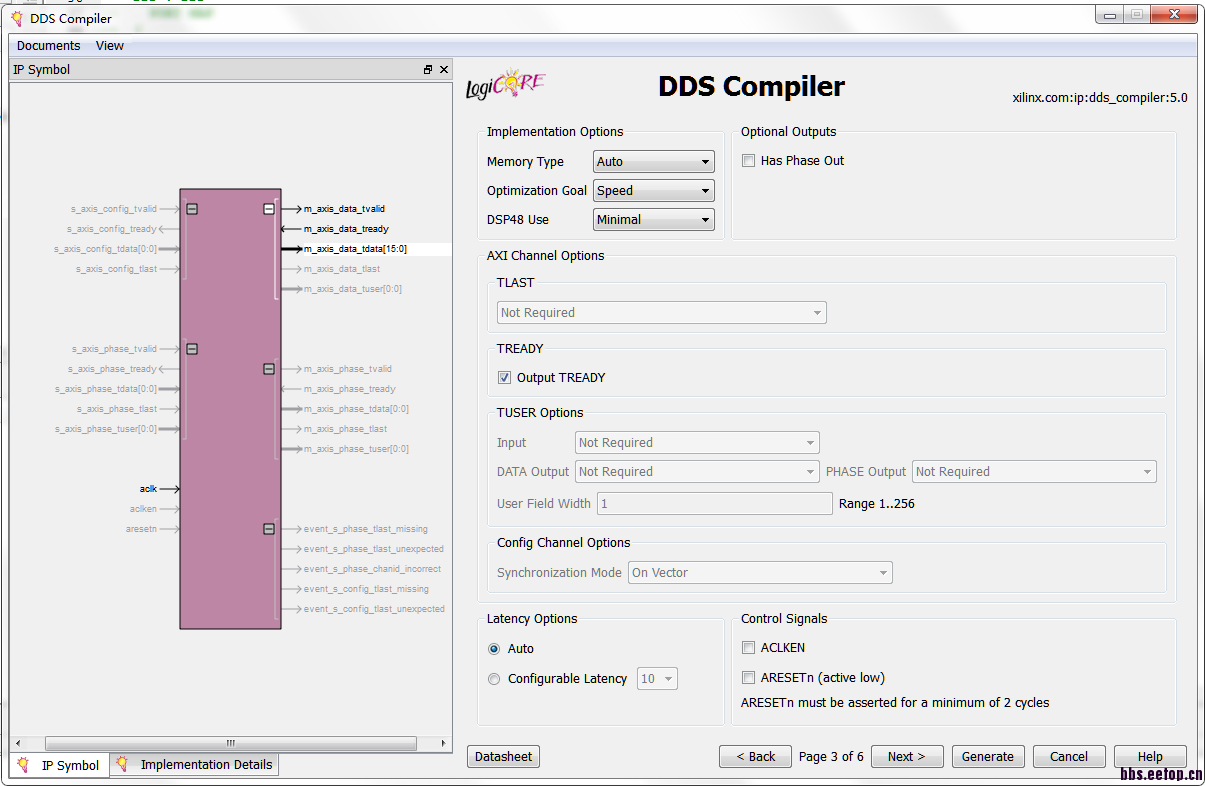

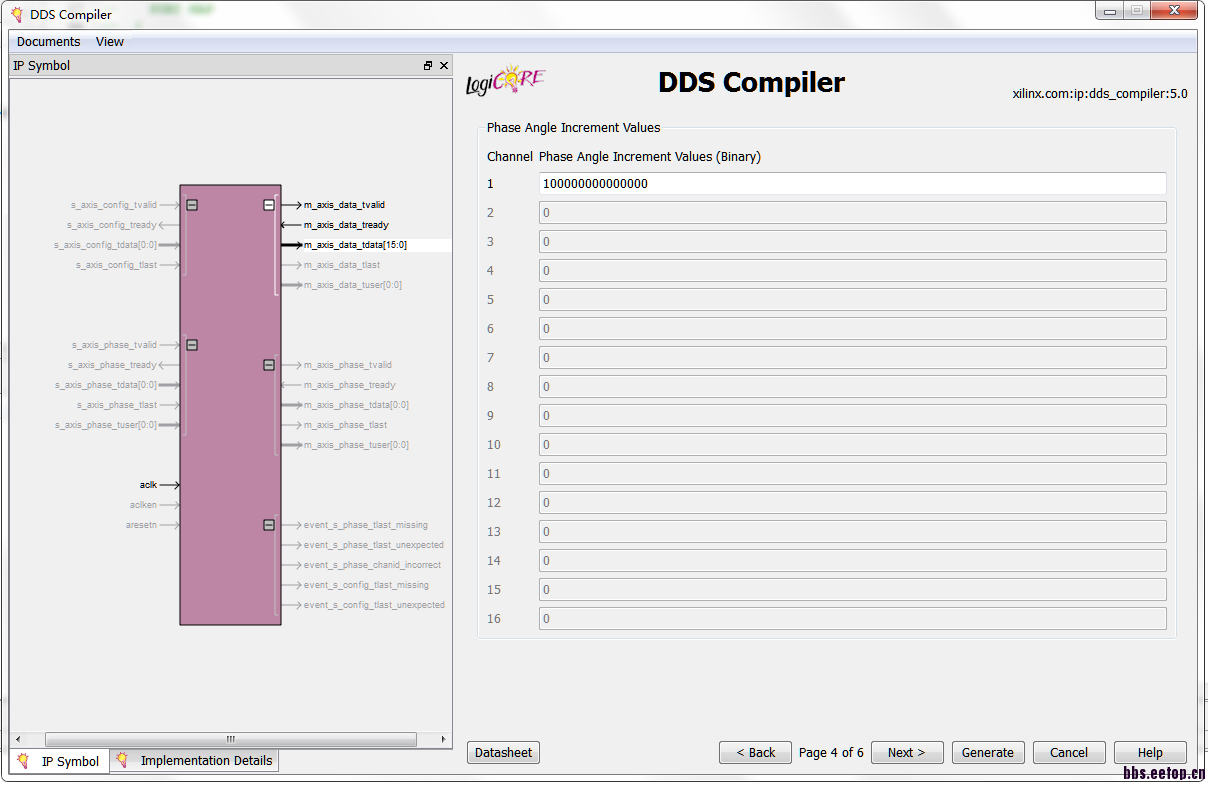

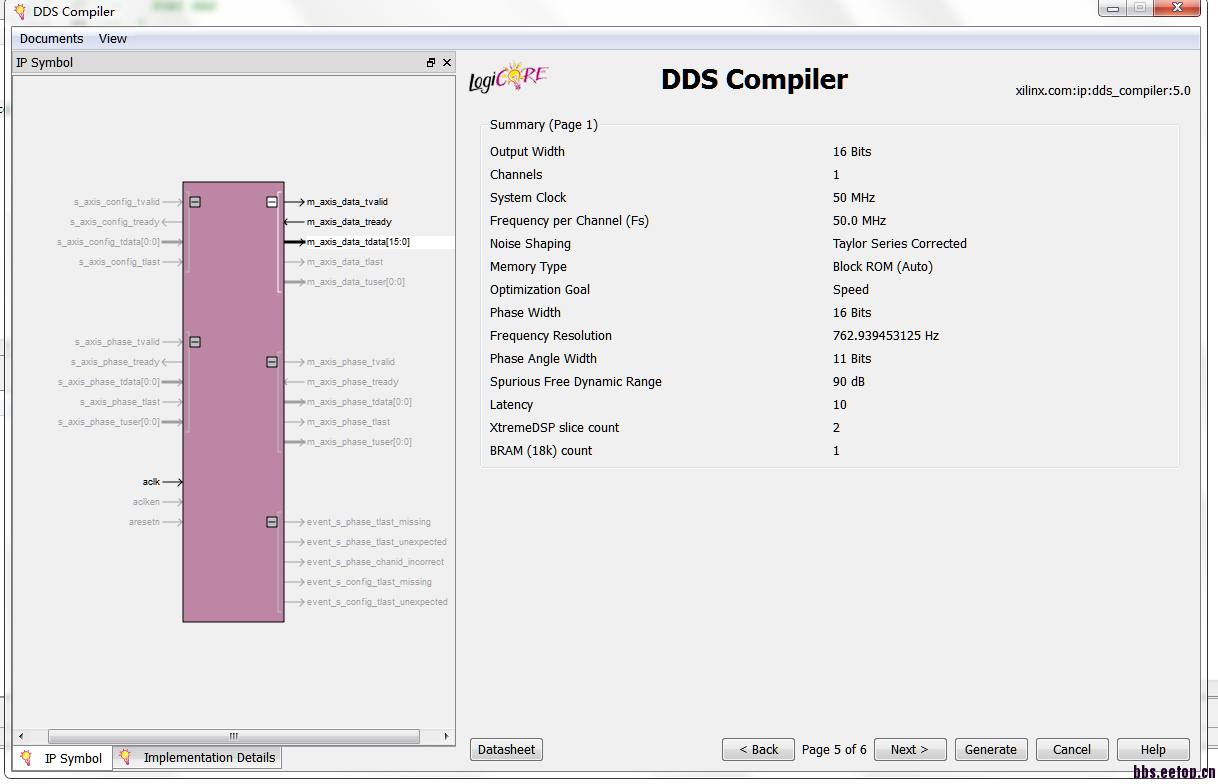

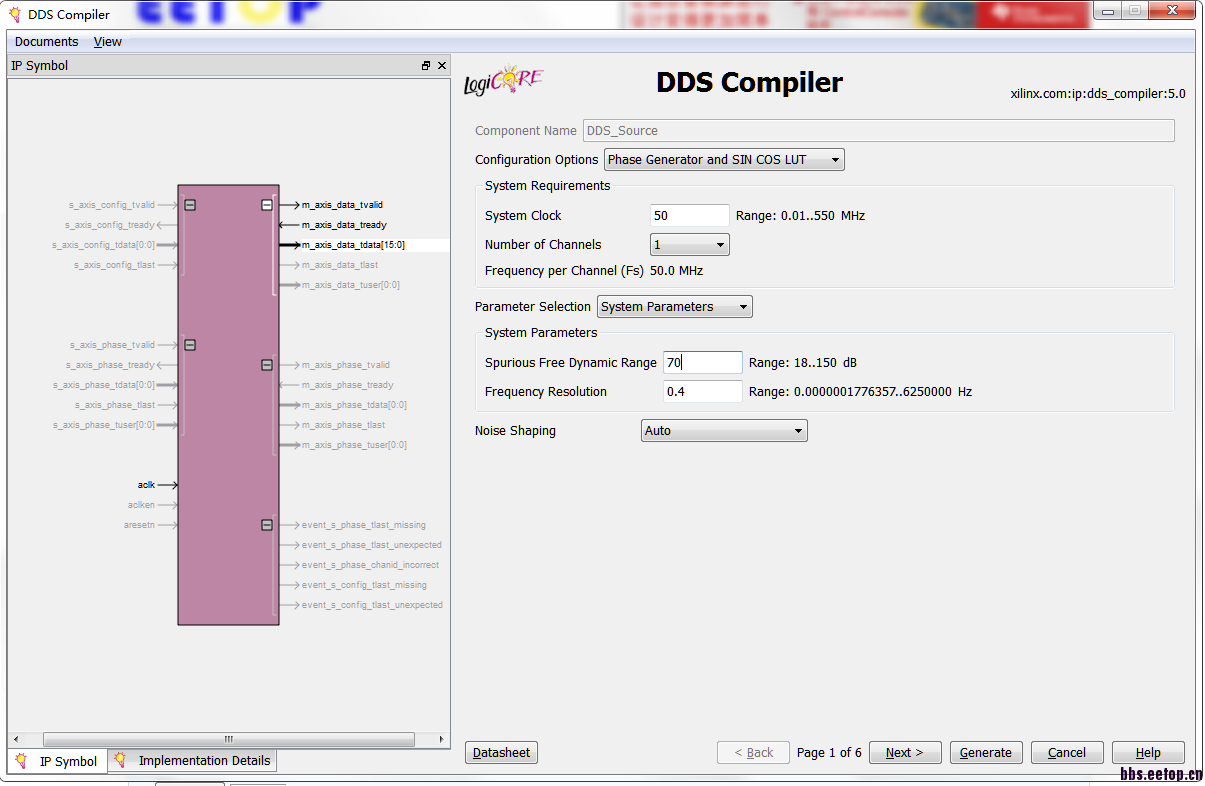

设置如下,外面给的aclk是50Mhz的,在这里要问一下,第一页System Clock是不是要和外面给的时钟一样?

或者使用system parameters

但就是无法得出标准的正玄波,chipscope的时钟是100M的,请高手指教啊。

好东西 看看

怎么没人理

System Clock是不是要和外面给的时钟一样

是的

但为什么出来的波形并不是标准的正弦波呢?

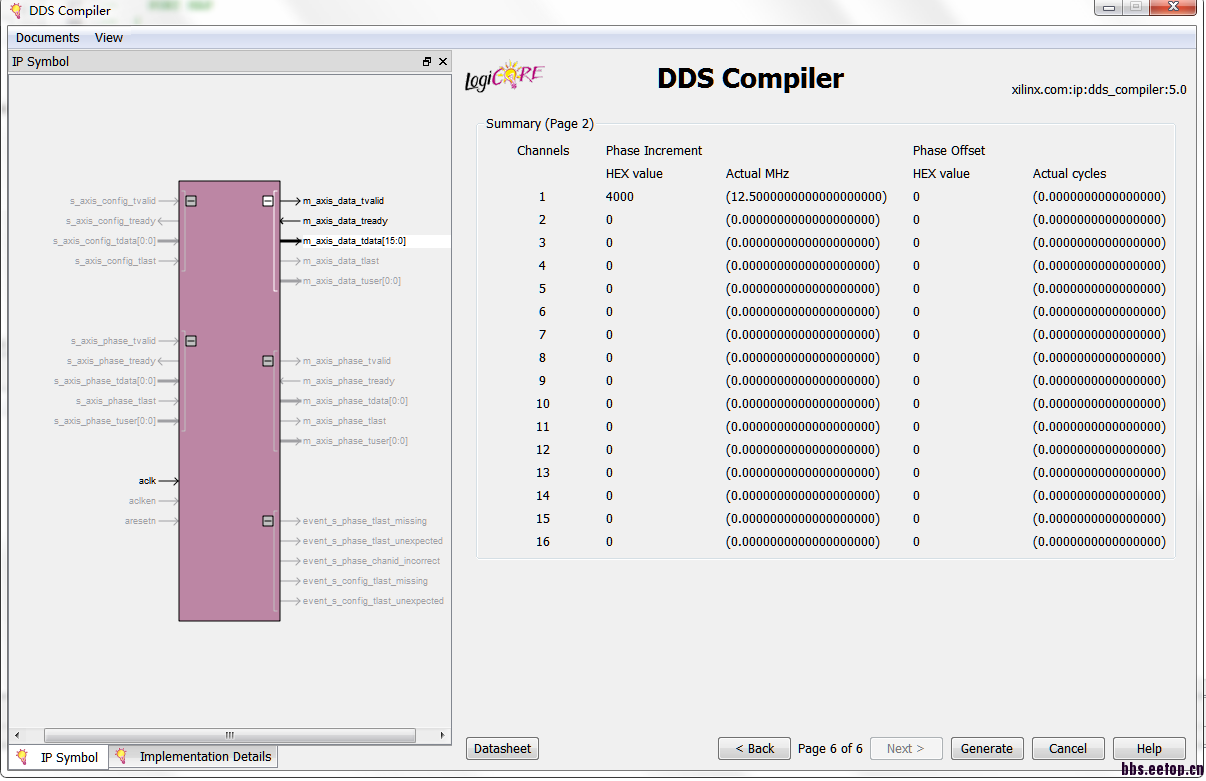

出现这种波形 应该是跟你设的incremental value 有关!

仿真过没有

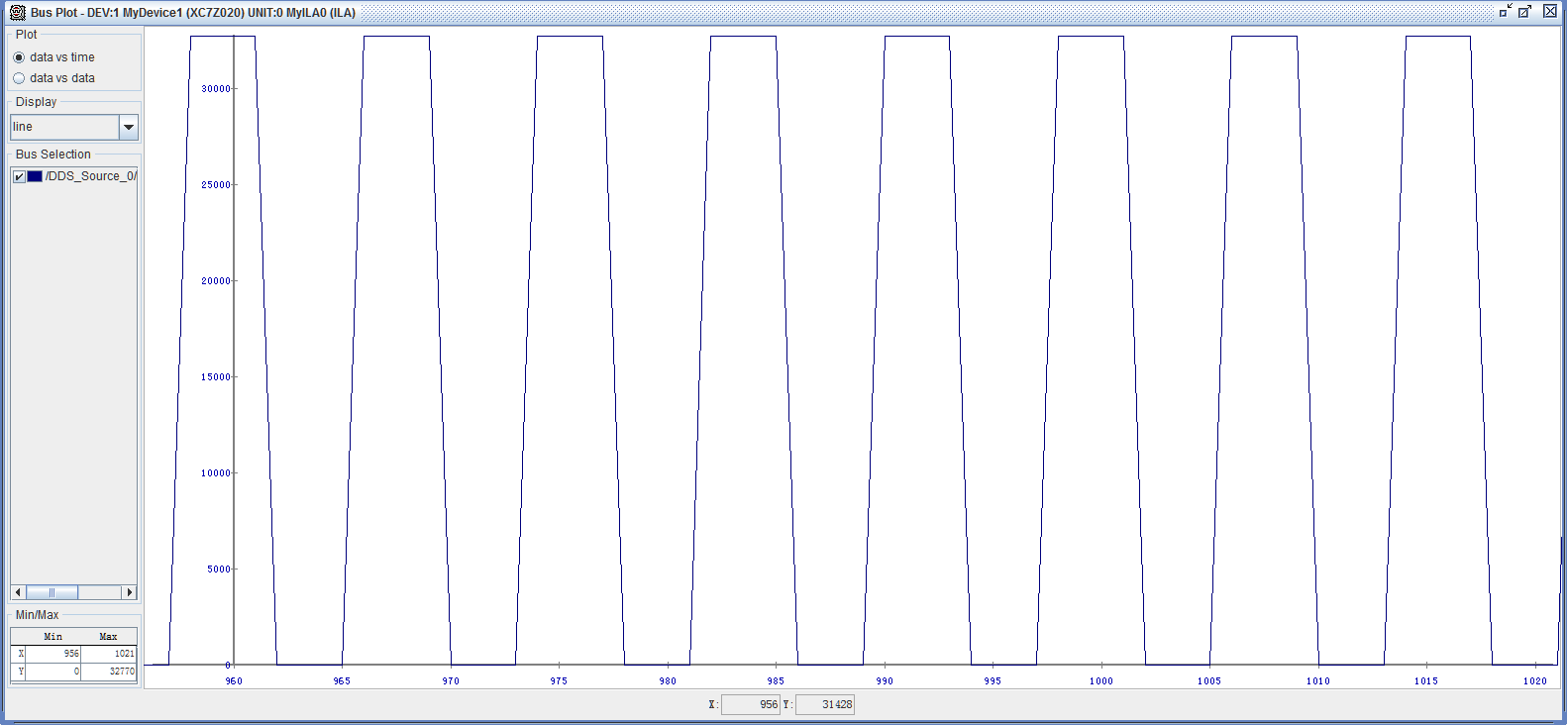

chipscope analyzer中数据的显示格式是选择什么呢?signed decimal/unsigned decimal/binay/hex选择不同的显示格式,画出来的波形也是不一样的,建议小编用signed的显示方式画一下试下

太感谢啦!以前一直使用默认16进制的,改成有符号十进制果然就好了

小编你好,我是fpga的初学者,我想请教一下你这个dds用modelsim仿真时测试文件是怎么写的?谢谢了

dds ip core输出的正余弦是有符号数,xilinx手册上没有说明

请问这个IP加入工程后怎么写相关的Verilog HDL代码?

我是来混点信元的

66666太6了!