综合时总是出现Warning: Output pins are stuck at VCC or GND

时间:10-02

整理:3721RD

点击:

编verilog程序时始终出现下面的警告:

Warning (13410): Pin "rx_data0[1]" is stuck at GND

Warning (13410): Pin "rx_data0[2]" is stuck at GND

Warning (13410): Pin "rx_data0[3]" is stuck at GND

Warning (13410): Pin "rx_data0[4]" is stuck at GND

Warning (13410): Pin "rx_data0[5]" is stuck at GND

Warning (13410): Pin "rx_data0[6]" is stuck at GND

Warning (13410): Pin "rx_data0[7]" is stuck at GND

Warning (13410): Pin "rx_data1[1]" is stuck at GND

Warning (13410): Pin "rx_data1[2]" is stuck at GND

Warning (13410): Pin "rx_data1[3]" is stuck at GND

Warning (13410): Pin "rx_data1[4]" is stuck at GND

Warning (13410): Pin "rx_data1[5]" is stuck at GND

Warning (13410): Pin "rx_data1[6]" is stuck at GND

Warning (13410): Pin "rx_data1[7]" is stuck at GND

Warning (13410): Pin "rx_data2[1]" is stuck at GND

Warning (13410): Pin "rx_data2[2]" is stuck at GND

Warning (13410): Pin "rx_data2[3]" is stuck at GND

Warning (13410): Pin "rx_data2[4]" is stuck at GND

Warning (13410): Pin "rx_data2[5]" is stuck at GND

Warning (13410): Pin "rx_data2[6]" is stuck at GND

Warning (13410): Pin "rx_data2[7]" is stuck at GND

Warning (13410): Pin "rx_data3[1]" is stuck at GND

Warning (13410): Pin "rx_data3[2]" is stuck at GND

Warning (13410): Pin "rx_data3[3]" is stuck at GND

Warning (13410): Pin "rx_data3[4]" is stuck at GND

Warning (13410): Pin "rx_data3[5]" is stuck at GND

Warning (13410): Pin "rx_data3[6]" is stuck at GND

Warning (13410): Pin "rx_data3[7]" is stuck at GND

Warning (13410): Pin "rx_data4[1]" is stuck at GND

Warning (13410): Pin "rx_data4[2]" is stuck at GND

Warning (13410): Pin "rx_data4[3]" is stuck at GND

Warning (13410): Pin "rx_data4[4]" is stuck at GND

Warning (13410): Pin "rx_data4[5]" is stuck at GND

Warning (13410): Pin "rx_data4[6]" is stuck at GND

Warning (13410): Pin "rx_data4[7]" is stuck at GND

不知道究竟哪里出问题了,寻高人指点,代码如下:

module data(

clk,rst_n,

rx_data_r,

rx_data0,rx_data1,rx_data2,rx_data3,rx_data4,

DATA_ready,DATA_EN,

reg_num

);

input clk; // 50MHz主时钟

input rst_n; //低电平复位信号

input DATA_ready;

input rx_data_r;

output[7:0] rx_data0; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data1; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data2; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data3; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data4; //接收数据寄存器,保存直至下一个数据来到

output DATA_EN;

output[5:0] reg_num;

reg[7:0] rx_data0;

reg[7:0] rx_data1;

reg[7:0] rx_data2;

reg[7:0] rx_data3;

reg[7:0] rx_data4;

reg[5:0] reg_num;

reg DATA_EN;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) DATA_EN <= 1'b0;

else begin

if(((rx_data_r == 8'b1) && (reg_num == 5'b0))|| (reg_num == 5'b00001) || (reg_num == 5'b00010)|| (reg_num == 5'b00011)|| (reg_num == 5'b00100)|| (reg_num == 5'b00101)) begin

DATA_EN <= 1'b1; //监测上位机是否发来控制信息

end

else DATA_EN <= 1'b0;

end

end

always @ (posedge DATA_ready or negedge rst_n) begin

if(!rst_n) reg_num <= 5'b0;

else begin

if(DATA_EN) begin

reg_num <= reg_num+1'b1;

if(reg_num == 5'b00110)begin

reg_num <= 5'b00000;

end

end

end

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

rx_data0 <= 8'b0;

rx_data1 <= 8'b0;

rx_data2 <= 8'b0;

rx_data3 <= 8'b0;

rx_data4 <= 8'b0;

end

else begin

if(DATA_EN) begin

case (reg_num)

5'b00001 :rx_data0 <= rx_data_r ; //锁存第一个数据

5'b00010 :rx_data1 <= rx_data_r ; //锁存第二个数据

5'b00011 :rx_data2 <= rx_data_r ; //锁存第三个数据

5'b00100 :rx_data3 <= rx_data_r ; //锁存第四个数据

5'b00101 :rx_data4 <= rx_data_r ; //锁存第五个数据

default: ;

endcase

end

end

end

endmodule

modelsim仿真library列表:

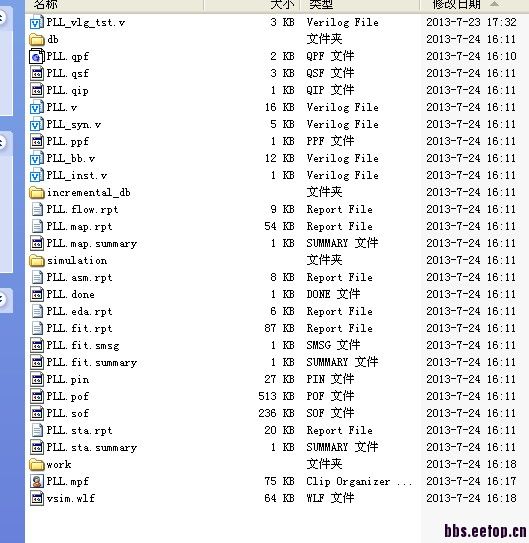

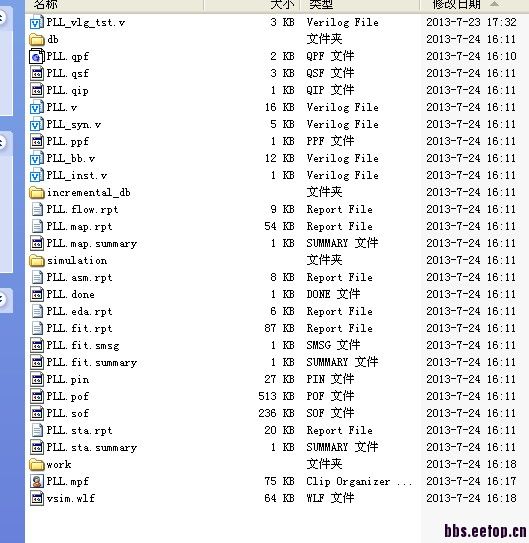

生成的文件列表:

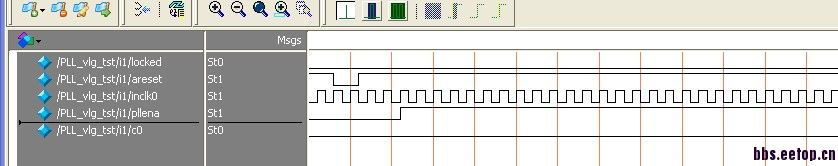

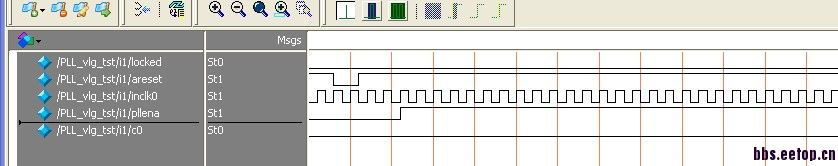

仿真结果图:

求指教。还有如果我要实例化这个锁相环的话,是不是只要把生成的PLL.v加入我的工程中,并实例化这个文件就行了么?

Warning (13410): Pin "rx_data0[1]" is stuck at GND

Warning (13410): Pin "rx_data0[2]" is stuck at GND

Warning (13410): Pin "rx_data0[3]" is stuck at GND

Warning (13410): Pin "rx_data0[4]" is stuck at GND

Warning (13410): Pin "rx_data0[5]" is stuck at GND

Warning (13410): Pin "rx_data0[6]" is stuck at GND

Warning (13410): Pin "rx_data0[7]" is stuck at GND

Warning (13410): Pin "rx_data1[1]" is stuck at GND

Warning (13410): Pin "rx_data1[2]" is stuck at GND

Warning (13410): Pin "rx_data1[3]" is stuck at GND

Warning (13410): Pin "rx_data1[4]" is stuck at GND

Warning (13410): Pin "rx_data1[5]" is stuck at GND

Warning (13410): Pin "rx_data1[6]" is stuck at GND

Warning (13410): Pin "rx_data1[7]" is stuck at GND

Warning (13410): Pin "rx_data2[1]" is stuck at GND

Warning (13410): Pin "rx_data2[2]" is stuck at GND

Warning (13410): Pin "rx_data2[3]" is stuck at GND

Warning (13410): Pin "rx_data2[4]" is stuck at GND

Warning (13410): Pin "rx_data2[5]" is stuck at GND

Warning (13410): Pin "rx_data2[6]" is stuck at GND

Warning (13410): Pin "rx_data2[7]" is stuck at GND

Warning (13410): Pin "rx_data3[1]" is stuck at GND

Warning (13410): Pin "rx_data3[2]" is stuck at GND

Warning (13410): Pin "rx_data3[3]" is stuck at GND

Warning (13410): Pin "rx_data3[4]" is stuck at GND

Warning (13410): Pin "rx_data3[5]" is stuck at GND

Warning (13410): Pin "rx_data3[6]" is stuck at GND

Warning (13410): Pin "rx_data3[7]" is stuck at GND

Warning (13410): Pin "rx_data4[1]" is stuck at GND

Warning (13410): Pin "rx_data4[2]" is stuck at GND

Warning (13410): Pin "rx_data4[3]" is stuck at GND

Warning (13410): Pin "rx_data4[4]" is stuck at GND

Warning (13410): Pin "rx_data4[5]" is stuck at GND

Warning (13410): Pin "rx_data4[6]" is stuck at GND

Warning (13410): Pin "rx_data4[7]" is stuck at GND

不知道究竟哪里出问题了,寻高人指点,代码如下:

module data(

clk,rst_n,

rx_data_r,

rx_data0,rx_data1,rx_data2,rx_data3,rx_data4,

DATA_ready,DATA_EN,

reg_num

);

input clk; // 50MHz主时钟

input rst_n; //低电平复位信号

input DATA_ready;

input rx_data_r;

output[7:0] rx_data0; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data1; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data2; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data3; //接收数据寄存器,保存直至下一个数据来到

output[7:0] rx_data4; //接收数据寄存器,保存直至下一个数据来到

output DATA_EN;

output[5:0] reg_num;

reg[7:0] rx_data0;

reg[7:0] rx_data1;

reg[7:0] rx_data2;

reg[7:0] rx_data3;

reg[7:0] rx_data4;

reg[5:0] reg_num;

reg DATA_EN;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) DATA_EN <= 1'b0;

else begin

if(((rx_data_r == 8'b1) && (reg_num == 5'b0))|| (reg_num == 5'b00001) || (reg_num == 5'b00010)|| (reg_num == 5'b00011)|| (reg_num == 5'b00100)|| (reg_num == 5'b00101)) begin

DATA_EN <= 1'b1; //监测上位机是否发来控制信息

end

else DATA_EN <= 1'b0;

end

end

always @ (posedge DATA_ready or negedge rst_n) begin

if(!rst_n) reg_num <= 5'b0;

else begin

if(DATA_EN) begin

reg_num <= reg_num+1'b1;

if(reg_num == 5'b00110)begin

reg_num <= 5'b00000;

end

end

end

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

rx_data0 <= 8'b0;

rx_data1 <= 8'b0;

rx_data2 <= 8'b0;

rx_data3 <= 8'b0;

rx_data4 <= 8'b0;

end

else begin

if(DATA_EN) begin

case (reg_num)

5'b00001 :rx_data0 <= rx_data_r ; //锁存第一个数据

5'b00010 :rx_data1 <= rx_data_r ; //锁存第二个数据

5'b00011 :rx_data2 <= rx_data_r ; //锁存第三个数据

5'b00100 :rx_data3 <= rx_data_r ; //锁存第四个数据

5'b00101 :rx_data4 <= rx_data_r ; //锁存第五个数据

default: ;

endcase

end

end

end

endmodule

rx_data_r只有1bit

rx_data是8bit

开头加一句

wire [7:0] rx_data_r;

我知道了,已经成功解决了,就一个小错误折腾了好多天啊!我qq是2314048725,欢迎大家交流

是的,就是这么解决的,就这么一个小漏洞,折腾了半天

这种错误其实可以在modelsim中仿真就可以发现的,不用等到综合才去看那么大一堆警告。

是啊,应该先modelsim仿真一下的,现在出现问题了,我现在用MegaWizard_Plug-in调用的PLL IP核,怎么用modelsim仿真啊?

当然可以仿真的,在quartus安装目录下有对应的仿真库的,PLL也是有的。先编译好库到modelsim中,仿真钢钢的。

可是我已经折腾两天了,还是没有仿真出来,库文件也添加了,就是没有波形出来。这是testbench代码:

- `timescale 1 ns/ 10 ps

- module PLL_vlg_tst();

- reg eachvec;

- reg areset;

- reg inclk0;

- reg pllena;

- // wires

- wire c0;

- wire locked;

- PLL i1 (

- .areset(areset),

- .c0(c0),

- .inclk0(inclk0),

- .locked(locked),

- .pllena(pllena)

- );

- always #10 inclk0=~inclk0;

- initial

- begin

- inclk0 =0;

- areset = 1'b1;

- pllena = 1'b0;

- #30 areset = 0;

- #30 areset = 1;

- #50 pllena = 1;

- end

- endmodule

modelsim仿真library列表:

生成的文件列表:

仿真结果图:

求指教。还有如果我要实例化这个锁相环的话,是不是只要把生成的PLL.v加入我的工程中,并实例化这个文件就行了么?

我需要信元而已,kanakn

大哥,它的areset是高电平复位,你一直给高电平,PLL一直复位着,怎么出波形哦?

有帮助