上电低电平复位电路negedge reset?

时间:10-02

整理:3721RD

点击:

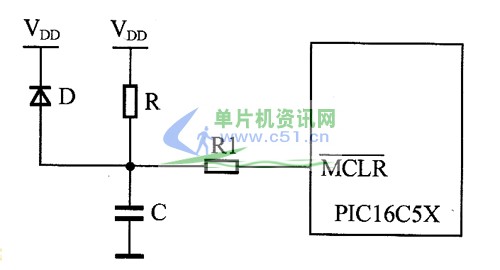

现在做的一个板子上不能手动复位,只能上电复位,而且是低电平复位。复位电路网络上很多,电源端接一个电阻,再串接一个电容,电容另一端接地,这电阻和电容之间的连接点再接一电阻连接到芯片复位reset端。

在verilog 代码中,有一个always 模块的敏感信号列表(negedge a or negedge reset)中其中a信号的跳变肯定不在上电处于低电平复位期间跳变的,可是分析复位电路只有一开始为低,之后升高 这样的一个变化跳变。似乎没有敏感列表中的 negedge reset 这样一个reset 下降沿跳变的过程,即,我的担忧是这个always 模块在reset处于低电平复位期间 模块执行不了,一些模块中的复位信号没有得到复位。

上面的问题及复位电路现象是测试我的上电复位电路 处于低电平复位时间时看到的,一上电根本没有reset 下降沿跳变过程,引起的质疑。希望和大家分析讨论。谢谢!

复位电路用的是这样的,之前文字叙述部分漏了二极管的叙述。是不是该复位电路不适合FPGA 的电平跳变呢?还是我测试复位电路时看到的现象不太对呢?又亦或是我对negedge reset 的理解过于“钻牛角”了或是不对呢?

在verilog 代码中,有一个always 模块的敏感信号列表(negedge a or negedge reset)中其中a信号的跳变肯定不在上电处于低电平复位期间跳变的,可是分析复位电路只有一开始为低,之后升高 这样的一个变化跳变。似乎没有敏感列表中的 negedge reset 这样一个reset 下降沿跳变的过程,即,我的担忧是这个always 模块在reset处于低电平复位期间 模块执行不了,一些模块中的复位信号没有得到复位。

上面的问题及复位电路现象是测试我的上电复位电路 处于低电平复位时间时看到的,一上电根本没有reset 下降沿跳变过程,引起的质疑。希望和大家分析讨论。谢谢!

我觉得是复位电路有问题

照那样的电路得到的信号是没有下降沿。

2# maclei

复位电路用的是这样的,之前文字叙述部分漏了二极管的叙述。是不是该复位电路不适合FPGA 的电平跳变呢?还是我测试复位电路时看到的现象不太对呢?又亦或是我对negedge reset 的理解过于“钻牛角”了或是不对呢?

还是 用专门的单稳器件复位比较好

4# gulouyin

可是上电复位电路的应用也是有成功先例的,没错的

..................................

又有朋友说,FPGA 一上电配置之后就是 复位状态 是吗?

看看。

老大,我有个FPGA问题困扰了好久,是SPARTAN 6的,可以加下我QQ么51512474,实在是有点崩溃,非常期待你加我!

照理說,RC充放電應該是從低電位到高電位,這時間依R & C 值決定,在低電位時應該會有一段不短的時間,除 非你的CLK這時都沒動作,不然應該會有 reset 在低電平的時間才對。