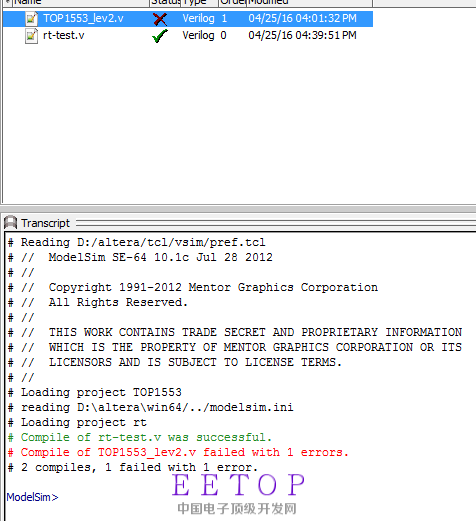

大家modelsim编译时遇到过这种问题吗?

时间:10-02

整理:3721RD

点击:

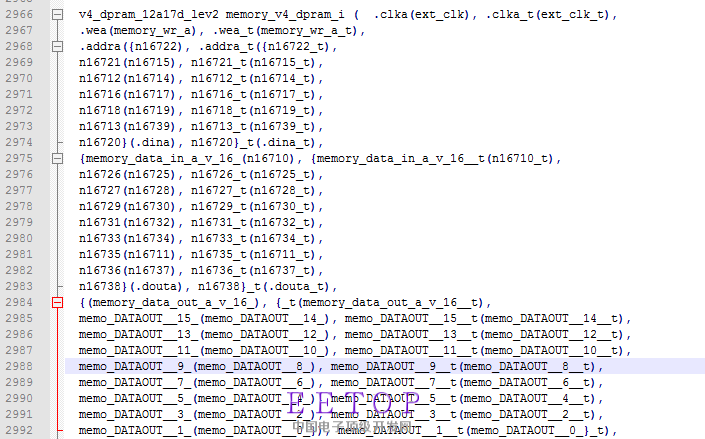

一看报错,原来是2968行那里 ,并口被综合成串口,里面有大括号

我是对工程代码加了glift逻辑(门级信息流追踪),就是所有端口、内部逻辑门的数据都做一个标记位“-t”,这样它发生了不可控制的变化时我可以看标记位是1还是0,得知是否被污染(改变)。

看了一下,其余模块的并口综合后都成了add1_,add1_t.....这样比较标准的格式。就在这里添加了逻辑后,成了这样的,我估计是因为v4模块是ram,打散后发生了quartus和modelsim不认识的变化

这和modelsim有什么关系?是你网表本身有问题,查查网表是什么工具产生的

是DC综合出来的。看了下,原因好像就是那种大括号。

奇怪的是,其余模块的并口打散成串口都是很规则的addr1,addr2,addr3...这样的,就这里还出来大括号了。

好像以前也碰到过类似问题,一是代码有错,二是DC版本,多试几个版本,三是脚本不合理。

我也碰到过类似问题,像是systemverilog 的支持问题。

不好解决啊。这个双口ram必须处于下层模块。要是在top层端口直接相连就好了。但他是top层下面的dpram层里面的模块。这综合就带了大括号。我醉了。

绝望ing