关于ise fft ip核的使用

时间:10-02

整理:3721RD

点击:

大家好,我现在在做一个fft变换,是用ise自带的fft核是实现的,但是仿真的时候输出总是出现高阻。ip核的rfd引脚也是高阻。望高手指教

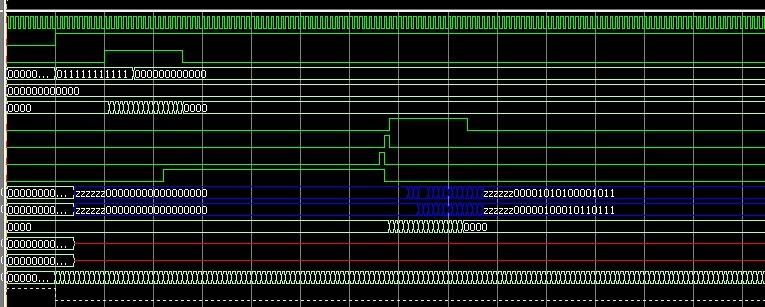

下面是仿真的截图

下面是仿真的截图

用过这个IP核,设置比较简单,应该没有问题!只要Start设置了就会出现数据

没用过这个IP, 你看一下输入的数据.

输入数据没问题的话, 输出如果有问题, 就从输入往里一级一级查看..

我想问一下start的设置是在测试程序里设置还是在主程序里设置

想请教一下,这个IP核是付费的吗?

还是免费的可以直接用?

可以直接用的,我用的是ISE10.1,里面自带的

谢谢,我正好有ISE10.1

安装试用一下 7# cxhappy

各个波形的名称都没有,实在不知道怎么看。

我想再请教一下,随着FFT点数变化,除了输出的位宽会变化外,还有什么会变化吗?我现在用1024点做,但是换了16点再做就不对了

这个问题,关注中。

为什么1024点结果正确,16点结果就不对呢?我现在知道start信号要比输入数据早输入四个时钟,但是持续时间究竟和点数有什么关系呢?我做16点的时候,试了一下,start的持续时间不同,输出结果就不同,不知道为什么。望大侠指教

我仿真的也没有输出,不知道是什么原因,Start的设置长度有限制吗?

您好 可以发一份代码给我么 谢谢您 13342404630@163.com