FPGA实现bpsk的解调中的问题,求助各路大神

时间:10-02

整理:3721RD

点击:

求助各路大神:1.准备用FPGA(xilinx spartan-6)来实现bpsk的解调,接收到中频频率为36M的信号,带宽为300K,通过采样速率为125Msps的ADC之后,需要通过抽取来降低采样频率吗?

2.整个实现过程需要设计哪些模块?据我所知,需要载波同步,符号同步,抽取和判决,帧同步等模块,请问还需要其他模块吗?

3.数字下变频的目的是不是就是实现解调?解调和下变频至零中频是不是同一个概念?

求大神解答,万分感激!

一个是采用正交解调,而另一个不是

2.整个实现过程需要设计哪些模块?据我所知,需要载波同步,符号同步,抽取和判决,帧同步等模块,请问还需要其他模块吗?

3.数字下变频的目的是不是就是实现解调?解调和下变频至零中频是不是同一个概念?

求大神解答,万分感激!

大神求解啊

中频蛮高的啊,还过采样。

我觉得数字下变频的目地就是实现解调,但解调和数字下变频不是一个概念

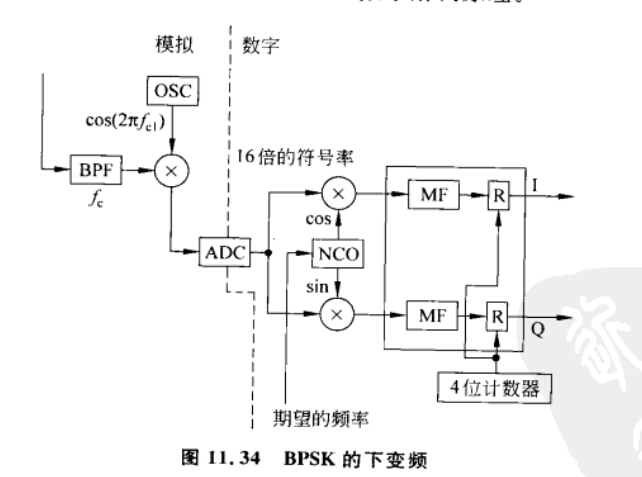

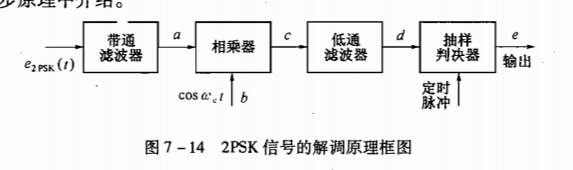

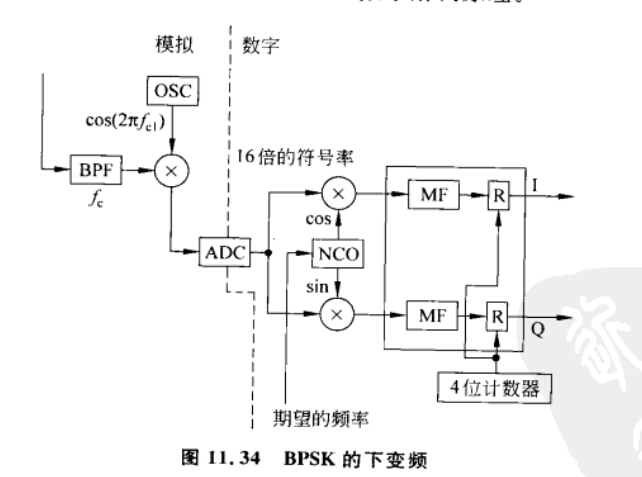

谢谢你的回答~还有个问题,就是bpsk解调为什么需要采用正交解调呢?请看如下两图:

一个是采用正交解调,而另一个不是

可以试试数据滤波和小波提取,小波具有正交特性

需要抽取滤波,载波同步是要做的,如果符号速率固定的话,符号同步会简单一些。

为什么要抽取滤波呢?你的符号速率是<300Ksps,经过AD量化后,一个符号,你用了大概500个点去表示,只有一个符号用一个点来表示,你才能判决后恢复原始序列,即信源。

简单的方法就是差分解调,性能差一点。视信号的性质,也可使用相干解调方法。