ise综合后,LUT中的输入顺序和真值表有问题,请各位帮忙看一下!

时间:10-02

整理:3721RD

点击:

刚刚开始学习verilog HDL,试着编写了几个小的程序,其中想要实现四个四入一出的LUT的小程序让我产生了很大的困惑,代码如下:

问题如下:

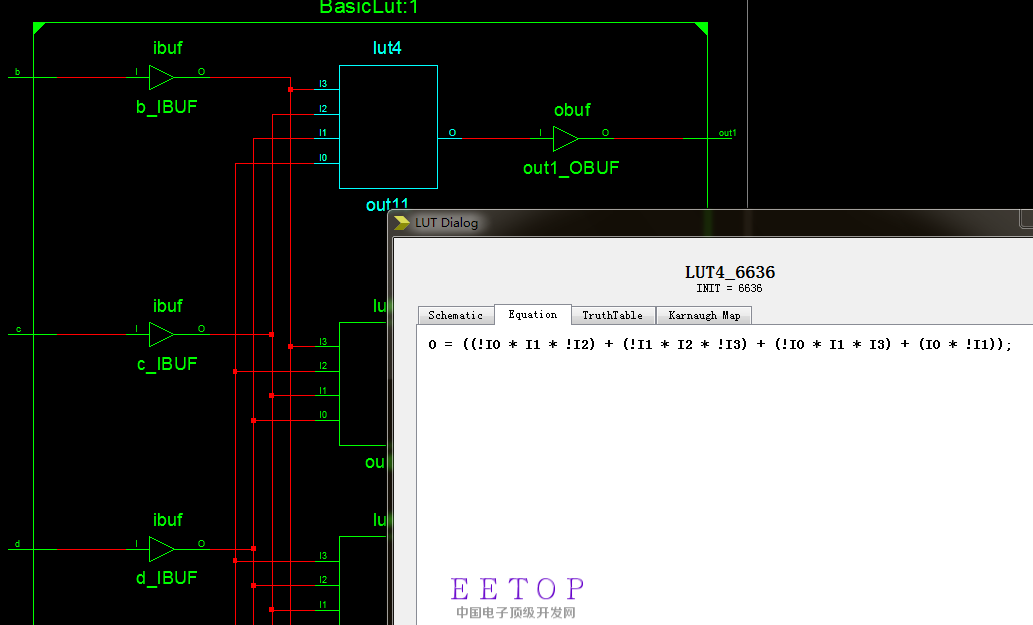

1、这张图左侧有四个输入,如何让它们按照abcd的顺序排布,而不是现在的bcda?

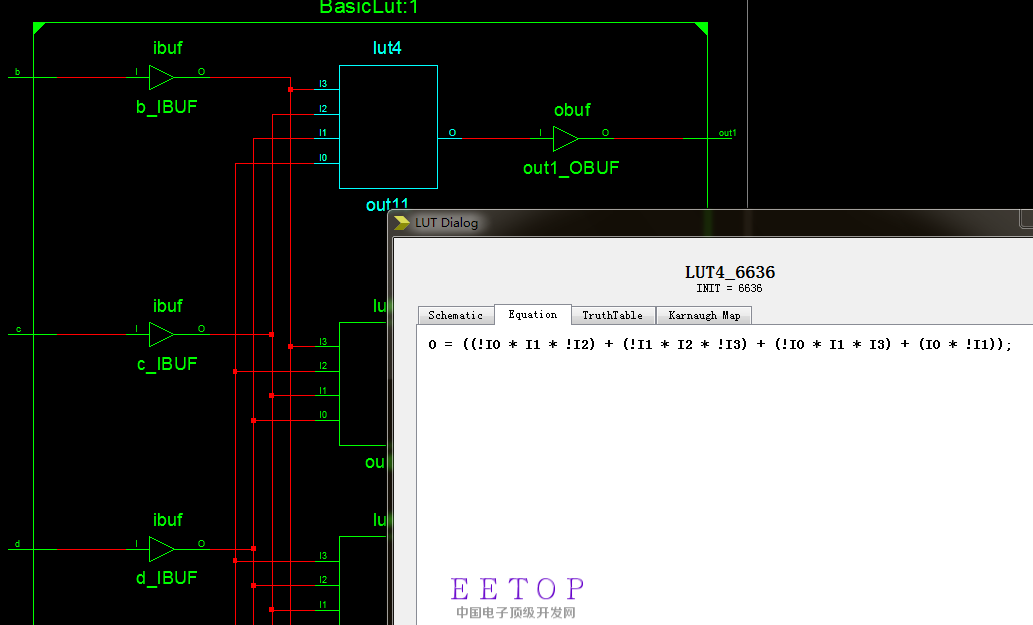

2、即便左侧的顺序不重要,但是我打开的第一个LUT的公式,因为我的理想是a对应I0,b对应I1,c对应I2,d对应I3,但是实际上第一个LUT中的顺序是a对应I0,d对应I1,c对应I2,b对应I3,所以按照这个公式计算出来的真值表和我想要的完全不一样。而其他三个LUT的顺序也是不正确的,并且和第一个中的adcb也是不同。我想请问,如何规定好abcd与I0I1I2I3之间的对应关系,使得我想要的真值表可以实现出来?

谢谢各位!

- module BasicLut(a,b,c,d,out1,out2,out3,out4);

- input a,b,c,d;

- output out1,out2,out3,out4;

- wire a,b,c,d;

- wire out1,out2,out3,out4;

- assign out1 = (a & ~d) | (~b & c & ~d) | (~a & ~c & d) | (~a & b & d);

- assign out2 = (a & ~b) | (~a & b & d) | (c & d);

- assign out3 = (~b & c) | (b & ~c & d) | (a & ~b & ~d) | (a & b & ~c);

- assign out4 = (b & d) | (b & c) | (~a & c & ~d) | (a & c & d);

- endmodule

问题如下:

1、这张图左侧有四个输入,如何让它们按照abcd的顺序排布,而不是现在的bcda?

2、即便左侧的顺序不重要,但是我打开的第一个LUT的公式,因为我的理想是a对应I0,b对应I1,c对应I2,d对应I3,但是实际上第一个LUT中的顺序是a对应I0,d对应I1,c对应I2,b对应I3,所以按照这个公式计算出来的真值表和我想要的完全不一样。而其他三个LUT的顺序也是不正确的,并且和第一个中的adcb也是不同。我想请问,如何规定好abcd与I0I1I2I3之间的对应关系,使得我想要的真值表可以实现出来?

谢谢各位!

顶一下

不懂,关注。

顶一下~