Select IO IP核仿真问题

时间:10-02

整理:3721RD

点击:

[attach]388611[/attach]

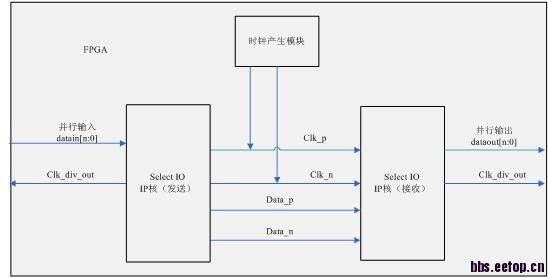

如图所示,在程序中调用两个SelectIO IP核,一个用于发送,另一个用于接收,n=7.

两个IP核的差分时钟信号由另一个时钟产生模块提供.仿真时,根据clk_div_out的周期改变并行输入datain的值,然后观察并行输出dataout

发现dataout的值与datain不相对应.在程序中通过移位操作dataout={dataout[1:0],dataout[7:2]},移位后dataout的大部分数据与datain相对应了,但还是有一些特殊点对应不上的.

为什么会出现这样的情况的,是我设计上存在问题,还是IP核没有设置好的?请大虾们指点指点

如图所示,在程序中调用两个SelectIO IP核,一个用于发送,另一个用于接收,n=7.

两个IP核的差分时钟信号由另一个时钟产生模块提供.仿真时,根据clk_div_out的周期改变并行输入datain的值,然后观察并行输出dataout

发现dataout的值与datain不相对应.在程序中通过移位操作dataout={dataout[1:0],dataout[7:2]},移位后dataout的大部分数据与datain相对应了,但还是有一些特殊点对应不上的.

为什么会出现这样的情况的,是我设计上存在问题,还是IP核没有设置好的?请大虾们指点指点

大神,你这接收端误码率是怎么降低的?