100M晶振产生外部时钟输入到FPGA,怎么在内部产生一个8.05M的时钟信号

时间:10-02

整理:3721RD

点击:

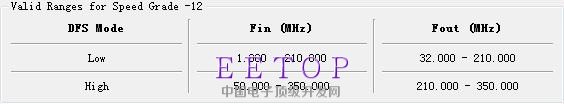

如题,尝试用了DCM的CLKFX接口,但是只能产生大于32M的时钟,求问大神如何解决的

外部用一个4兆左右的时钟,DCM不支持生成时钟小于原始时钟

先看芯片手册,每款芯片的DCM 和PLL 输入输出频率都有范围,确认8.05在可用范围内后再看能不能分出来了。

可以用逻辑分出一个8.05M的脉冲做为高频时钟的使能信号来做相关8.05M的控制

10M分频为5M,然后产生

我电路上的FPGA外部只接了100M晶振,无法输入其他频率的时钟,8.05M只能用这个100M时钟产生

我电路上的FPGA外部只接了100M晶振,不支持再输入其他频率的时钟,8.05M时钟只能通过100M来产生

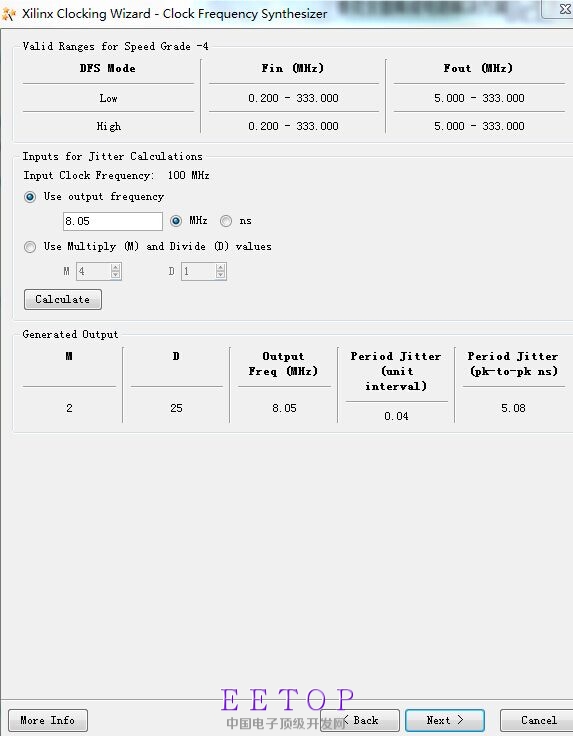

我怎么发现可以哈

100*2/25=8,而不是8.05

是不是不同的FPGA是不一样的,我用的是v4sx35的,你用的是什么芯片

对头 ,我还没有注意到这一点,产生不了8.05M,用sp3

如果必须要精确的用8.05M,可以采用内插数据的方法

正解

你用的这是什么FPGA芯片?V5?

可以试试用芯片内部的锁相环PLL电路,我以前用48MHZ输出40MHZ就是用的PLL,40=48*5/6

建议换时钟源

计数分频不可以吗

又受教了!