EDK中ucf问题

映射时提示如下,需要限定IOSTANDARD for IOBUFDS,如何解决。

LIT:600 - IOBUFDS symbol "u_ddr2/u_ddr2_top_0/u_mem_if_top/u_phy_top/u_phy_io/gen_dqs[0].u_iob_dqs/gen_dqs_iob_ddr2.u_iobuf_dqs" (output signal=u_ddr2/u_ddr2_top_0/u_mem_if_top/u_phy_top/u_phy_io/gen_dqs[0].u_iob_d qs/dqs_ibuf) does not have IOSTANDARD specified. Map is unable to generate a default IOSTANDARD for IOBUFDS, one has to be explicitly provided.

dqs_ibuf是rtl的ddr2_phy_dqs_iob文件中的信号,我在UCF给出了NET "*/gen_dqs

你用的是哪个芯片?用哪个引脚?

找到例化IOBUF的那个文件,在例化IOBUF的参数中有IO_STANDARD,在那里修改应该可以

您好,我是这样添加的约束

IOBUFDS #

(

.IOSTANDARD("DIFF_SSTL18_II_DCI")

)

u_iobuf_dqs

(

.O (dqs_ibuf),

.IO (ddr_dqs),

.IOB (ddr_dqs_n),

.I (dqs_out),

.T (dqs_oe_n_r)

);

这个原语没有问题。此外,UCF中还需要对“ddr_dqs”和“ddr_dqs_n”添加相同的IO_STANDARD约束,但中间信号“dqs_ibuf”不应添加IO_STANDARD约束

我在ISE中建立了一个工程,其中用到了mig IP核,将整个工程作为一个外设挂在EDK下,其中综合时会报错The I/O component has an illegal IOSTANDARD value. The IOB component is configured to use single-ended signaling and can not use differential IOSTANDARD value DIFF_SSTL18_II_DCI. Two ways to rectify this issue are: 1) Change the IOSTANDARD value to a single-ended standard. 2) Correct the I/O connectivity by instantiating a differential I/O buffer.

ddr2_dqs和ddr2_dqs_n的所有信号都会报此错误。该工程在ISE中综合时并没有任何问题。其中设计这两个信号的地方为

module ddr2_phy_dqs_iob

IOBUFDS u_iobuf_dqs

(

.O (dqs_ibuf),

.IO (ddr_dqs),

.IOB (ddr_dqs_n),

.I (dqs_out),

.T (dqs_oe_n_r)

);

它的上一层文件中

genvar dqs_i;

generate

for(dqs_i = 0; dqs_i < DQS_WIDTH; dqs_i = dqs_i+1) begin: gen_dqs

ddr2_phy_dqs_iob #

(

.DDR_TYPE (DDR_TYPE),

.HIGH_PERFORMANCE_MODE (HIGH_PERFORMANCE_MODE),

.IODELAY_GRP (IODELAY_GRP)

)

u_iob_dqs

(

.clk0 (clk0),

.clkdiv0 (clkdiv0),

.rst0 (rst0),

.dlyinc_dqs (dlyinc_dqs[dqs_i]),

.dlyce_dqs (dlyce_dqs[dqs_i]),

.dlyrst_dqs (dlyrst_dqs),

.dlyinc_gate (dlyinc_gate[dqs_i]),

.dlyce_gate (dlyce_gate[dqs_i]),

.dlyrst_gate (dlyrst_gate[dqs_i]),

.dqs_oe_n (dqs_oe_n),

.dqs_rst_n (dqs_rst_n),

.en_dqs (en_dqs[dqs_i]),

.ddr_dqs (ddr_dqs[dqs_i]),

.ddr_dqs_n (ddr_dqs_n[dqs_i]),

.dq_ce (dq_ce[dqs_i]),

.delayed_dqs (delayed_dqs[dqs_i])

);

end

endgenerate

再上层文件是对其实例化ddr_dqs->ddr2_dqs

ddr2_dqs_n->ddr2_dqs_n

我的ucf中对信号的约束为

NET "ddr2_dqs

NET "ddr2_dqs_n

我搜了一些论坛的帖子,但是还么有找到解决的办法。请问您觉得这种错误会是什么原因?

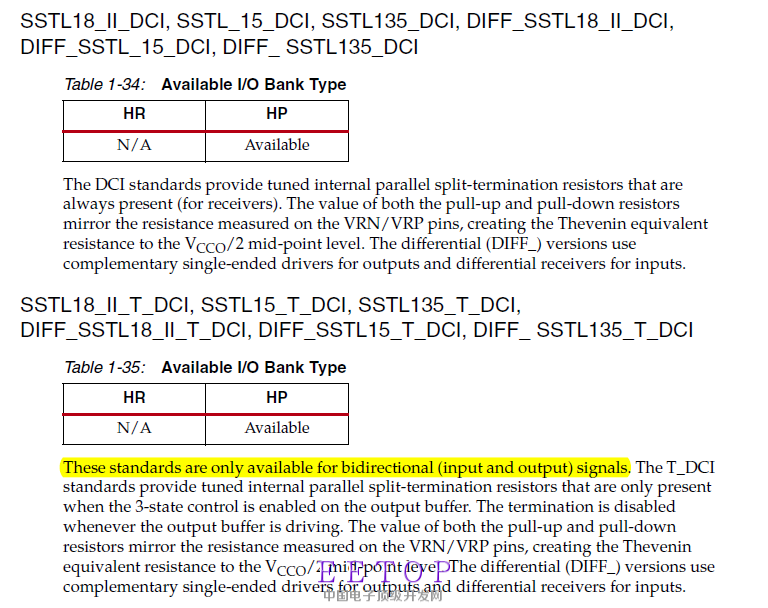

双向信号的IOSTANDARD似乎应该是后缀为*_T_DCI的,你把IOSTANDARD改成SSTL18_II_T_DCI试试?虽然跟报的错好像不是一个……从Select IO手册里截的图: