ISE MAP 时间长,请大家帮忙看看!

时间:10-02

整理:3721RD

点击:

目前遇到一件暂不知道怎么处理的困难:

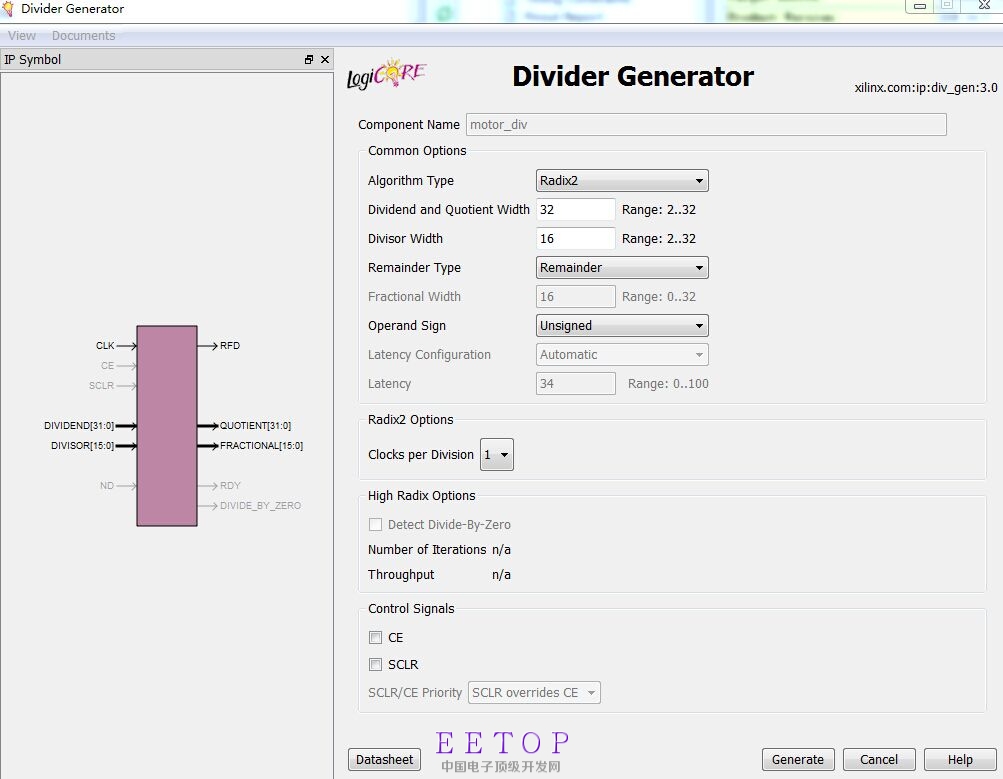

在spartan6 xc6slx25器件上一个程序,目前编译时间在20小时左右,资源利用在55%;其它资源也利用不多(资源都不紧张);目前最大的问题是编译时间相当长,程序应该也不算很复杂,程序里有几个步进电机控制程序,包含除法器等。

ISE的设置都采用通用设置,里面有个ddr3约束了下时钟,其它没有时序约束处理。

目前怀疑除法器导致程序编译时间变长,但不知如何处理或设置,来这里请教大家了。

有遇到同样问题的兄弟帮忙说说,谢谢!

在spartan6 xc6slx25器件上一个程序,目前编译时间在20小时左右,资源利用在55%;其它资源也利用不多(资源都不紧张);目前最大的问题是编译时间相当长,程序应该也不算很复杂,程序里有几个步进电机控制程序,包含除法器等。

ISE的设置都采用通用设置,里面有个ddr3约束了下时钟,其它没有时序约束处理。

目前怀疑除法器导致程序编译时间变长,但不知如何处理或设置,来这里请教大家了。

有遇到同样问题的兄弟帮忙说说,谢谢!

你这编译时间还真是长,你是第二天快下班的时候它才编译完?

1、我的建议是把你怀疑的地方先注释掉看看。

2、如果找到了,你可以把这一块功能单独用一个。v写,或者换一个时钟。

恩,之前做个一些实验,把步进电机驱动模块去掉之后,时间会明显短一些(步进电机驱动程序包含除法器IP和开方根IP)

有可能是你的除法器之类的IP没有设置multicycle吧。除数和被除数不会每个cycle都会变化吧

确实每时钟周期计算一次

IP核

1.spartan6-25器件,正常来说(lut reg 占用率均在75%以下),20分钟足矣

2.造成par太慢的原因,可能是时序不满足,导致par重复布局布线

3.你的资源只占用了55%,因此可能是你的时钟设计的不好,建议梳理一下时钟的设计

最后解决了吗?

先把你的sdc spec 條件放寬試試...有可能是你的spec太難routing了

就从小编描述而言,map时间过长是由于你约束不完整,或者代码存在比较大的timing violation, 所工具在不断的进行尝试,你可以看下ise map的 phase,一般来讲 15个phase 就可以跑完,如果你的timing 质量很差,那工具会根据你所选择的策略不断的进行优化