verilog宏功能模块在modelsim仿真错误

代码还可以这样写么?

一个文件里这样写不出错么?

endmodule

module

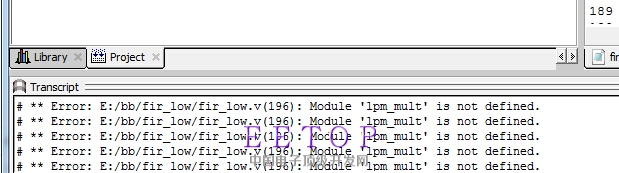

额 , 没问题把,主模块和子模块关系没事吧,我verilog编译通过了不是说的很明白嘛,lpm_mult这个module没有定义。看看filelist是否忘记添加这个模块之类的小错误

QuartusII 是支持一个文件中多个module。不知道modelsim支不支持。

首先当然不是拆分文件,首先看看你的调用。top放到后面去试试

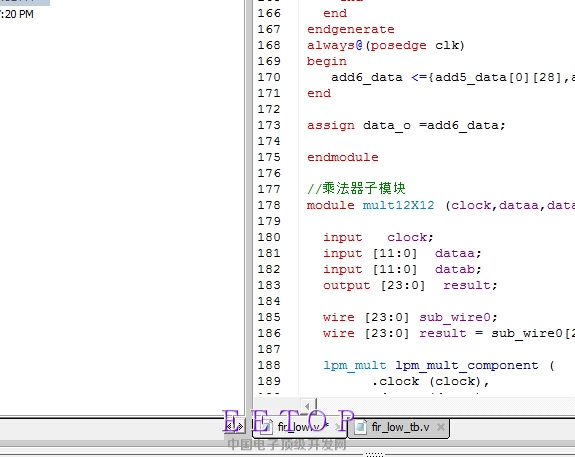

module mult12X12 (clock,dataa,datab,result);

input

clock;

input

[11:0] dataa;

input

[11:0] datab;

output

[23:0] result;

wire [23:0] sub_wire0;

wire [23:0] result = sub_wire0[23:0];

lpm_mult

lpm_mult_component (

.clock (clock),

.dataa (dataa),

.datab (datab),

.result (sub_wire0),

.aclr (1'b0),

.clken (1'b1),

.sum (1'b0));

defparam

lpm_mult_component.lpm_hint = "MAXIMIZE_SPEED=5",

lpm_mult_component.lpm_pipeline = 1,

lpm_mult_component.lpm_representation = "SIGNED",

lpm_mult_component.lpm_type = "LPM_MULT",

lpm_mult_component.lpm_widtha = 12,

lpm_mult_component.lpm_widthb = 12,

lpm_mult_component.lpm_widthp = 24;endmodule

这个就是我那个verilog产生的宏功能模块,这种代码不像verilog,我都看不懂。lpm_mult这个也是模块吗,能详细说一下怎么搞吗,还有你说得那个表在哪

module mult12X12 (clock,dataa,datab,result);

input

clock;

input

[11:0] dataa;

input

[11:0] datab;

output

[23:0] result;

wire [23:0] sub_wire0;

wire [23:0] result = sub_wire0[23:0];

lpm_mult

lpm_mult_component (

.clock (clock),

.dataa (dataa),

.datab (datab),

.result (sub_wire0),

.aclr (1'b0),

.clken (1'b1),

.sum (1'b0));

defparam

lpm_mult_component.lpm_hint = "MAXIMIZE_SPEED=5",

lpm_mult_component.lpm_pipeline = 1,

lpm_mult_component.lpm_representation = "SIGNED",

lpm_mult_component.lpm_type = "LPM_MULT",

lpm_mult_component.lpm_widtha = 12,

lpm_mult_component.lpm_widthb = 12,

lpm_mult_component.lpm_widthp = 24;endmodule

这个就是我用verilog产生的宏功能模块,这个我看不懂,都不像verilog,lpm_mult这个也是模块吗,能具体说一下一个怎么做吗

你意思是不是说不要子模块,把它合并到主模块里面

lpm_mult 这个module的.v文件是否在工程中?

不是,是modelsim比QuartusII 要傻一点。你引用的模块要先声明,要在前面,后面才是你的top。

类似于C语言中,子函数在前面写,主函数man在最后面。

我把那个子模块放在主模块前面还是不行,还是提示lpm_mult这个,lpm_mult我不知道是怎么,怎么弄

仿真的时候还需要把altera相应的仿真库加载上,lpm_mult定义是在仿真库文件里面

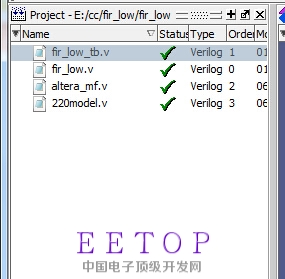

我加了220model和altera_mf两个,是这两个吗?然后modelsim仿真我找不到要看的端口名,怎么办,图片在楼下

就是这样,我加了那两个库,但是却找不到我的输入和输出端口,请问怎么回事

不太清楚具体环境,log里面不就是说

lpm_mult lpm_mult_component(...) 调用有问题么,

说找不到lpm_mult 这个模块,

lpm_mult.v这个文件在哪?

我加了两个库,编译什么的通过的,就是想看波形的时候没有我被测试程序的端口

仿真的时候不要开启优化选项,就是vsim命令需要加上-novopt

额,我对modelsim不大熟,,你说的这些命令我没见过,也不知道怎么用,可以说详细点吗,谢谢

你的modelsim仿真是从QuartusII 中启动的,还是另外新建立的modelsim工程呢