关于verilog综合后逻辑优化的问题

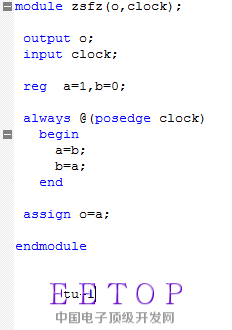

图-1

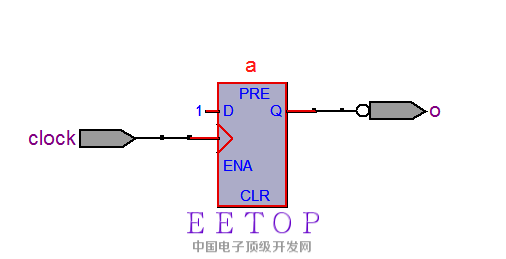

图-11

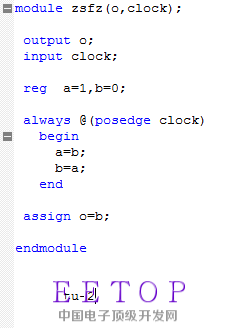

图-2

图-2

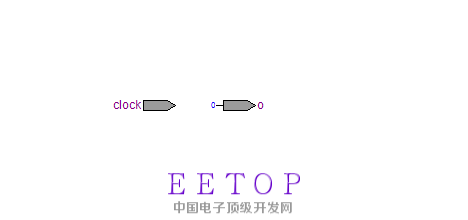

图-22

上图中图-1代码综合成图-11,图-2代码综合成图-22

代码简单易懂,两个代码唯一不同之处就是一个输出为o=a;一个o=b(无论是哪个代码电路,输出都为0);但是逻辑综合优化后电路居然那么大的差别。

求各位前辈指点指点

在always里面应该使用非阻塞赋值,阻塞赋值写法本身就有问题

this is blocking and non blocking coding style.

你用的综合软件是什么啊?

我查了一下,说是可以使用阻塞和非阻塞赋值,但是不能混合使用。代码很简单,综合出来的电路结果也没错,但是电路结构相差太大了,求解释一下

quartus。这个是FPGA的,ASIC的我在学习中,刚装完个DC,能用您的语言解释一下quartus和DC综合的区别么?

Thank you for answering my question.You mean, I used the wrong code style, so the integrated circuit is difference? But the circuit function is right, will not be the comprehensive optimization of the defects?

想了会,突然意识到:

Verilog HDL叫什么?

叫做硬件描述语言,硬件描述!描述的是硬件哦!

小编的写法,或许没有语法错误,但代表什么,不知道,

或许各个解释工具、综合软件对其定义不一样。

就如一句经典的话:不想当裁缝的厨师不是好士兵!

有语法错误么,没有!什么意思呢,或许是哲学问题吧~

我想要这样的逻辑,所以用这样的写法,然后去综合,那么结果就是我期望的,类似这种感觉吧~

所以,建议按照我们能明确综合结果(或者仿真结果)的风格来写代码。

比如阻塞非阻塞规定,比如同步异步复位规定。

谢谢你打那么多字,受教良多~