Xilinx Vertix-5 FPGA开发板怎么输出1.8V的电压

时间:10-02

整理:3721RD

点击:

V5开发板右侧的6排PIN,能够通过ISE的设置,把原来的2.5V或者3.3V变成1.8V的输出吗?

这6排PIN,在管脚图里面连的VCCO是不同的,左边三排,第一排接地,中间的那排接VCC3V3或者VCC2V5,第三排接VCC2V5;

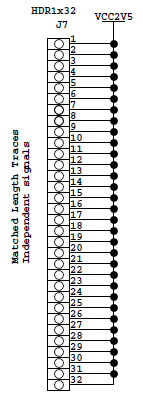

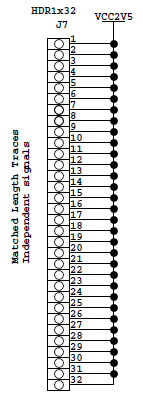

右边3排,第一排的前4个接VCC5V,接着四个接VCC3V3,剩下的都接VCC2V5,中间的那排都接地,最右边那排可以接VCC3V3或者VCC2V5,如下图是左边三排最靠右边的那一排的管脚图:

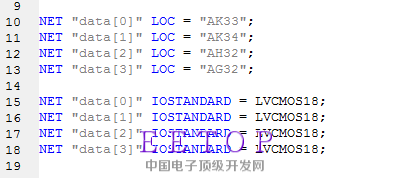

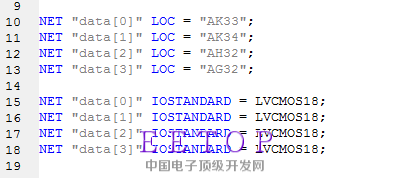

我在ucf文件里对最右排的其中四个引脚进行约束,想把这四个引脚的输出变成1.8V,但发现设置不起作用,把代码烧到FPGA板里,触发后用万用表一测,高电平依旧是3.3V

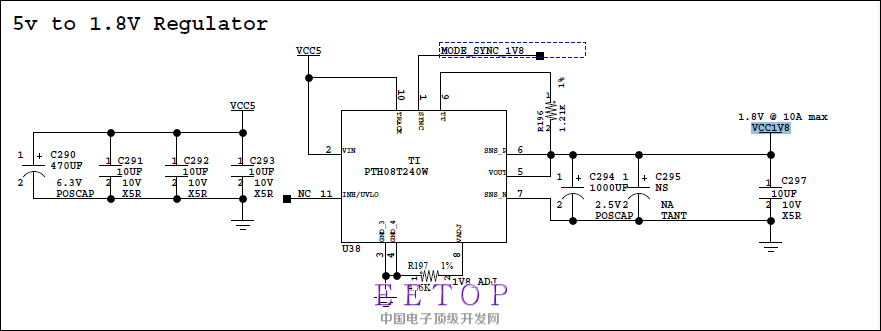

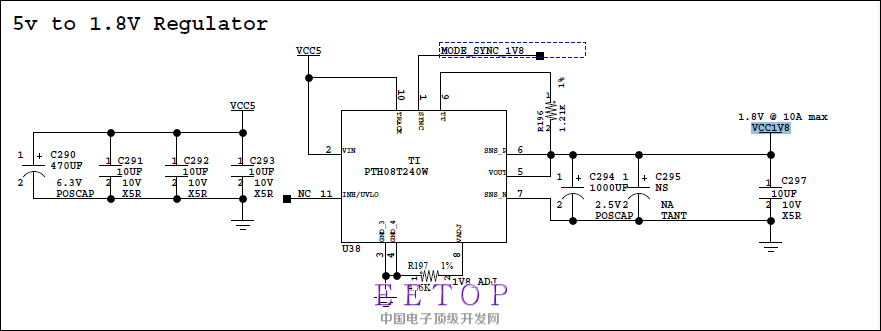

所以有没有大神用过V5的板子,这个板子上的PIN都不能输出1.8V的电压吗,但我发现管脚图里面有相应的变压器:

我需要50多个可用的IO口,这6排的PIN脚总共192个,可以满足了,就是不知道怎么设置把它们的输出和输入变成1.8V

求助大神们!

这6排PIN,在管脚图里面连的VCCO是不同的,左边三排,第一排接地,中间的那排接VCC3V3或者VCC2V5,第三排接VCC2V5;

右边3排,第一排的前4个接VCC5V,接着四个接VCC3V3,剩下的都接VCC2V5,中间的那排都接地,最右边那排可以接VCC3V3或者VCC2V5,如下图是左边三排最靠右边的那一排的管脚图:

我在ucf文件里对最右排的其中四个引脚进行约束,想把这四个引脚的输出变成1.8V,但发现设置不起作用,把代码烧到FPGA板里,触发后用万用表一测,高电平依旧是3.3V

所以有没有大神用过V5的板子,这个板子上的PIN都不能输出1.8V的电压吗,但我发现管脚图里面有相应的变压器:

我需要50多个可用的IO口,这6排的PIN脚总共192个,可以满足了,就是不知道怎么设置把它们的输出和输入变成1.8V

求助大神们!

名字打错了,是Virtex-5,抱歉

是不是需要调整FPGA Bank电压?

硬件上如果把bank的vcco电源已经接了3.3V,是没有办法通过软件来改成1.8和2.5的电平的。

我觉得应该需要调整bank上的电压来选择,约束的作用只是和bank的电压配合,无法改变实际的电压值。

”V5开发板右侧的6排PIN,能够通过ISE的设置,把原来的2.5V或者3.3V变成1.8V的输出吗?“

这个回答是一定不可以,约束永远不可能改变硬件现实情况,相反,是硬件现实情况决定了约束,这个要理解的。

如果你想改变IO的电压,只有一个方法,找到那几个bank,从硬件上飞线(有跳线就最好,否则就得强制飞线),把对应bank的VCCIO管脚,在PCB板上飞线或者跳线倒1.8V上。

看看硬件原理图吧,这种一般都有相应的开关之类的可以设置选择不同的bank电压,我们这边的板子就是通过焊接不同的电阻来选择bank 电压。

小编,你好,IO输出电压一般是由相应BANK供电决定的,软件配置是改变不了的。除非你调节一下BANK供电电压。

楼至用的是哪个开发板,能分享一下原理图不?先谢谢了!