spartan6的flash固化问题

时间:10-02

整理:3721RD

点击:

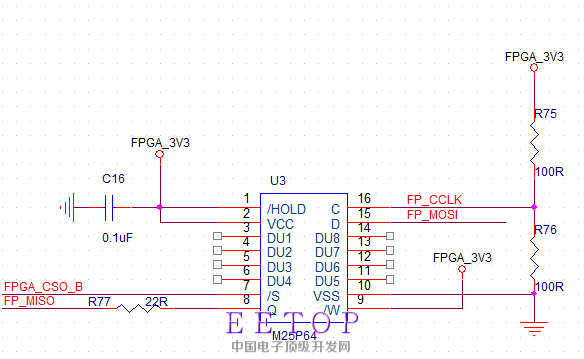

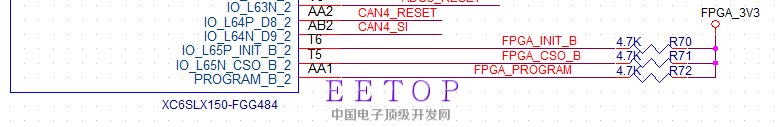

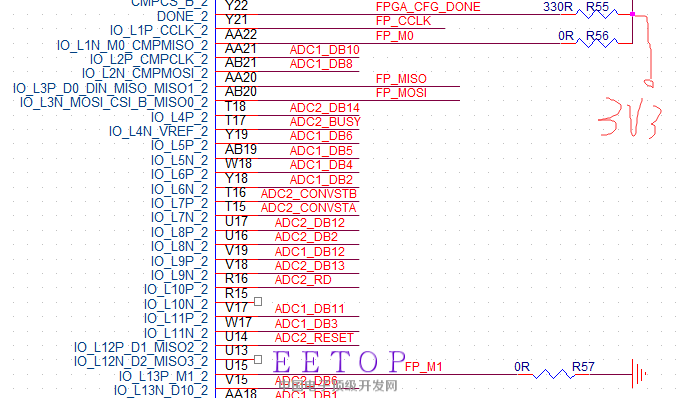

各位坛友们,最近在做一个FPGA的项目,用的是spartan6的芯片,可以直接把代码下到FPGA中,但是不能把代码固化在FLASH里面,提示错误见图,FLASH用的是M25P128,主串模式,参考手册设计的电路。以前没有用过SPI FLASH,所以不知道问题出在哪里,我用示波器抓了下CLK和CE的波形,上面的是CLK,下面的是CE,波形是在我给FLASH下代码的时候抓出来的,可是为什么连出现的时钟都是不连续的?困扰我两天了,各位坛友们能不能说说是哪里出了问题,谢谢了~

CLK(绿色)的毛刺是因为 示波器的探针引起的

SPI时序不太对吧,你把SI、SO, CS, SCLK,都抓出来看看

你的CLK更像是数据信号

很奇怪,为什么这个图上 时钟还没出现的时候数据就出来了。

我感觉就是这个时钟不对,可是我用的是主串模式,这个时钟是FPGA提供出来的才对 呀,为什么会这样呢?

你的spi master 是 FPGA 实现的 还是外面的烧录器?

在你没有烧写FPGA时,应该不存在FPGA里面有SPI MASTER啊

还是说你先烧写了FPGA,然后再通过FPGA里的spi mater去写 flash ?

不管怎样,电阻拿掉,确定master的设备(烧写器 or FPGA) 点在上面 看没有负载时,master命令发的对不对。

你的报错信息中说检验ID失败了,读到的ID都是0,说没有发现spi flash,但是从输出的时钟波形看,像是下载进fpga的那个jtag转flash烧写的小软核出问题了。你抓到的波形应该是小软核在读flash的ID,你可以对照m25p64的手册看看RDID指令,应该要输出32个clk才对,这里只有8个,对不上。

先确认配置这块的电路设计没有连接错误,生成mcs文件的步骤没有错误,实在不行再换个版本的ise试试。

可以高兴一下,把ISE14.2换成了13.2,果然可以烧进FLASH了,但是烧写的速度太慢了,基本上15分钟左右才能烧完,但是真的烧进去了。

我在烧FLASH的时候,用示波器抓了一下FLASH的时钟,发现还是和上面的时钟一样的, 然后我同时抓JTAG的时钟,我发现烧FLASH的时钟和JTAG的时钟是同一个时钟,都是那样一段一段的。

这两个时钟应该是连接在一起的