Xilinx Simple Dual-port BRAM仿真问题

时间:10-02

整理:3721RD

点击:

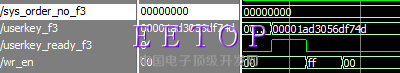

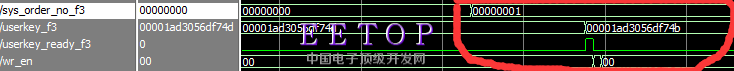

,求助个问题,在用Xilinx的IP核生成simple-dualport-ram仿真时,顺序写入三个数据后,再读,无论读地址给的是0,1,还是2,读出的永远是ram里最后一条数据。这是什么问题?图1是往地址0里写入...4d,图2是往地址1里写入4b。

,求助个问题,在用Xilinx的IP核生成simple-dualport-ram仿真时,顺序写入三个数据后,再读,无论读地址给的是0,1,还是2,读出的永远是ram里最后一条数据。这是什么问题?图1是往地址0里写入...4d,图2是往地址1里写入4b。 但是读的时候无论读地址给什么值,读出的永远是RAM的最后一条数据,求教。

但是读的时候无论读地址给什么值,读出的永远是RAM的最后一条数据,求教。

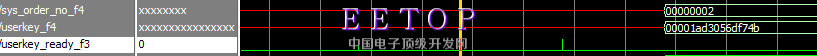

生成IP核时,如果选上Enabled 32-bit address,则wra信号位宽为8,控制数据的读写时是按字节控制的,即byte-writes模式;未选择Enabled 32-bit address,则wra信号位宽永远为1,高为写,低可读,正常情况下选该模式即可。最初犯错误是因为外部输入地址是32位,没有很好理解Enabled 32-bit address的含义,就勾选上了,导致最终的错误。RAM读写地址的宽度是生成IP核时所选的深度确定的。