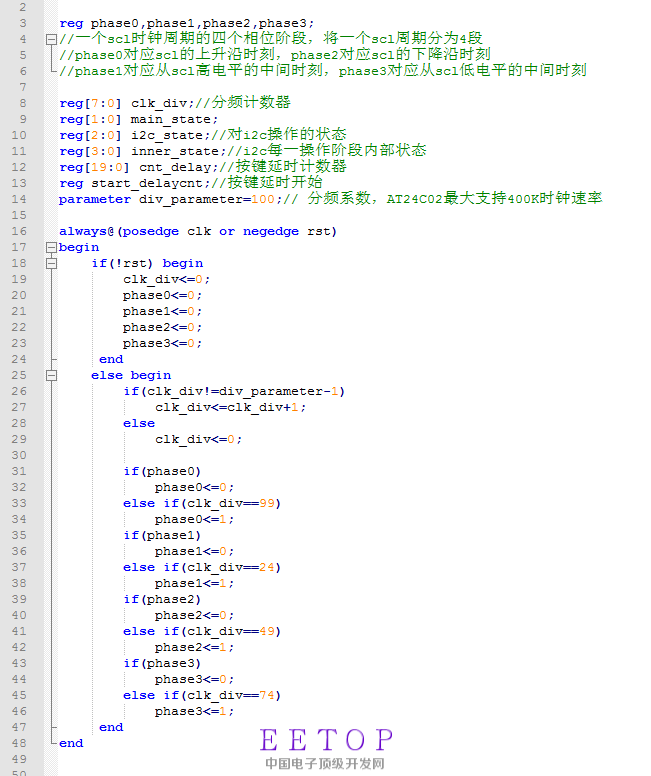

下面这段verilog代码我看不懂结构。求大神帮助

时间:10-02

整理:3721RD

点击:

从第31行开始就不懂了。

感觉好凌乱。求大神帮助

难道是刚用完这个状态就马上再下一个上升沿就复位?

编译会通过吗? 感觉语法就有问题

代码上面不是有说明吗

不同触发器的赋值写到了一个always块里,这个是能编译通过且综合的,只不过代码不太规范,可能是为了方便。每一对if elseif 是对一个触发器的赋值,不同if-elseif间是并行关系。懂了没?

(1)counter:0-99计数 (100 cycle)

(2)phase0 : 计数器到99拉高1cycle后再拉低。与计数0相同时间拉高。 指示0相位

(3)phase1 : 计数器到24拉高1cycle后再拉低。与计数25相同时间拉高。指示90度相位

(4)phase2 : 计数器到49拉高1cycle后再拉低。与计数50相同时间拉高。指示180度相位

(5)phase3 : 计数器到74拉高1cycle后再拉低。与计数75相同时间拉高。指示270度相位;

PS:把数字换成宏定义可读性多一些。

换点积分。