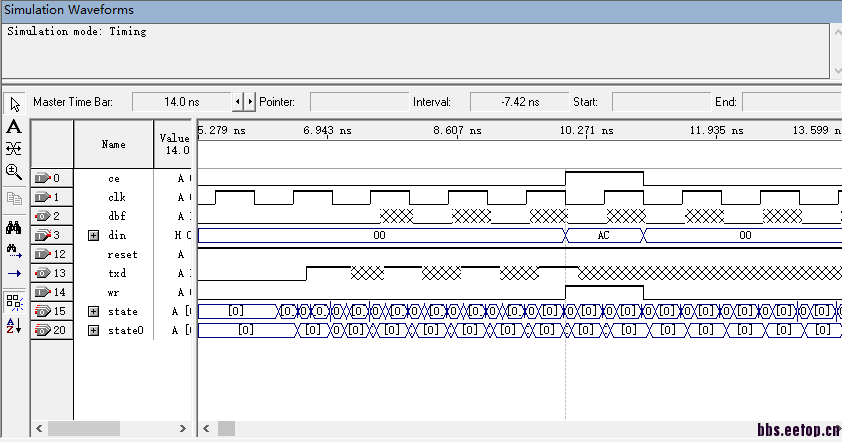

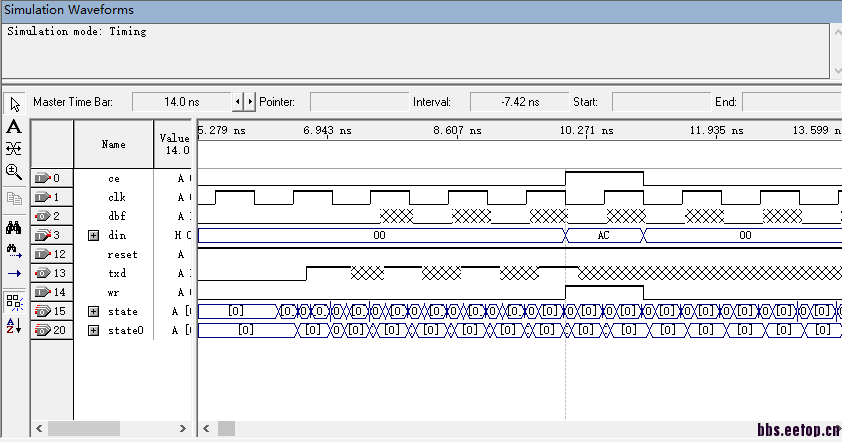

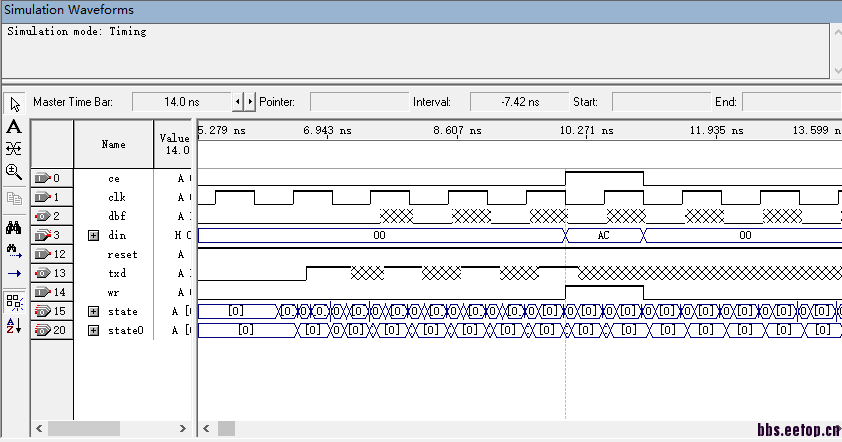

verilog编译通过,但是仿真出问题了

时间:10-02

整理:3721RD

点击:

module tx(clk,din,reset, wr,ce,dbf, txd,state,state0);

input clk,reset ,wr,ce;

//clk=11.0592MHz

//baud=11.0592Mhz/12=921.6kHz

input [7:0]din;

output txd,dbf;output [3:0] state;output [1:0] state0;

reg[7:0] data;

reg[9:0] shift;

reg[4:0] count,t;

reg [3:0] state;

reg [1:0] state0;

reg dbf,tbr; // dbf--data buffer full. tbr--transmit buffer ready.

wire txd;

assign txd=shift[0];

always@(posedge clk)

if (reset==0)

state0<=0;

else

case(state0)

2'b00:begin

if(wr==1 && ce==1)

begin state0<=1;data<=din;end

if(tbr==1) //发送数据准备好

state0<=2;

end

2'b01:if(wr==0 || ce==0)

begin dbf<=1;state0<=0;end

2'b10:begin dbf<=0;state0<=0;end

endcase

always@(posedge clk)

if (reset==0)

begin state<=0; shift[0]<=1;end

else

case(state)

4'b0000:if(t==11 && dbf==1)

begin

tbr<=1; state<=1;t<=0;

shift[9]<=1;

shift[8:1]<=data[7:0];

shift[0]<=0; //bit0:start bit

end

else

if (t<11) t=t+1;

4'b0001: if(t==11) //bit1:d0

begin shift<=shift>>1; shift[9]<=1; state<=2;t<=0; tbr<=0; end

else

t<=t+1;

4'b0010: if(t==11) //bit2:d1

begin shift<=shift>>1; shift[9]<=1; state<=3;t<=0; end

else

t<=t+1;

4'b0011: if(t==11) //bit3:d2

begin shift<=shift>>1; shift[9]<=1; state<=4;t<=0; end

else

t<=t+1;

4'b0100: if(t==11) //bit4:d3

begin shift<=shift>>1; shift[9]<=1; state<=5;t<=0; end

else

t<=t+1;

4'b0101: if(t==11) //bit5:d4

begin shift<=shift>>1; shift[9]<=1; state<=6;t<=0; end

else

t<=t+1;

4'b0110: if(t==11) //bit6:d5

begin shift<=shift>>1; shift[9]<=1; state<=7;t<=0; end

else

t<=t+1;

4'b0111: if(t==11) //bit7:d6

begin shift<=shift>>1; shift[9]<=1; state<=8;t<=0; end

else

t<=t+1;

4'b1000: if(t==11) //bit8:d7

begin shift<=shift>>1; shift[9]<=1; state<=9;t<=0; end

else

t<=t+1;

4'b1001: if(t==11) //bit9:stop

begin shift<=shift>>1; shift[9]<=1; state<=0;t<=0; end

else

t<=t+1;

default

begin t<=0; state<=0;end

endcase

endmodule

input clk,reset ,wr,ce;

//clk=11.0592MHz

//baud=11.0592Mhz/12=921.6kHz

input [7:0]din;

output txd,dbf;output [3:0] state;output [1:0] state0;

reg[7:0] data;

reg[9:0] shift;

reg[4:0] count,t;

reg [3:0] state;

reg [1:0] state0;

reg dbf,tbr; // dbf--data buffer full. tbr--transmit buffer ready.

wire txd;

assign txd=shift[0];

always@(posedge clk)

if (reset==0)

state0<=0;

else

case(state0)

2'b00:begin

if(wr==1 && ce==1)

begin state0<=1;data<=din;end

if(tbr==1) //发送数据准备好

state0<=2;

end

2'b01:if(wr==0 || ce==0)

begin dbf<=1;state0<=0;end

2'b10:begin dbf<=0;state0<=0;end

endcase

always@(posedge clk)

if (reset==0)

begin state<=0; shift[0]<=1;end

else

case(state)

4'b0000:if(t==11 && dbf==1)

begin

tbr<=1; state<=1;t<=0;

shift[9]<=1;

shift[8:1]<=data[7:0];

shift[0]<=0; //bit0:start bit

end

else

if (t<11) t=t+1;

4'b0001: if(t==11) //bit1:d0

begin shift<=shift>>1; shift[9]<=1; state<=2;t<=0; tbr<=0; end

else

t<=t+1;

4'b0010: if(t==11) //bit2:d1

begin shift<=shift>>1; shift[9]<=1; state<=3;t<=0; end

else

t<=t+1;

4'b0011: if(t==11) //bit3:d2

begin shift<=shift>>1; shift[9]<=1; state<=4;t<=0; end

else

t<=t+1;

4'b0100: if(t==11) //bit4:d3

begin shift<=shift>>1; shift[9]<=1; state<=5;t<=0; end

else

t<=t+1;

4'b0101: if(t==11) //bit5:d4

begin shift<=shift>>1; shift[9]<=1; state<=6;t<=0; end

else

t<=t+1;

4'b0110: if(t==11) //bit6:d5

begin shift<=shift>>1; shift[9]<=1; state<=7;t<=0; end

else

t<=t+1;

4'b0111: if(t==11) //bit7:d6

begin shift<=shift>>1; shift[9]<=1; state<=8;t<=0; end

else

t<=t+1;

4'b1000: if(t==11) //bit8:d7

begin shift<=shift>>1; shift[9]<=1; state<=9;t<=0; end

else

t<=t+1;

4'b1001: if(t==11) //bit9:stop

begin shift<=shift>>1; shift[9]<=1; state<=0;t<=0; end

else

t<=t+1;

default

begin t<=0; state<=0;end

endcase

endmodule

急求 在线等 这会不知道是不是都睡觉了啊

你可能要添加一些信息,会更容易让别人帮忙分析。一般的,特别是有工作经验的人,都只有上班前5分钟左右看帖子,5分钟之内分析不出来,往往就跳下一个帖子了。所以,提供更多的信息,有助于解决你的问题。

1. 最好简单描述你这个代码中的问题 ,至少你自己知道,哪里是不对的,哪怕是你不知道代码哪里不对,只知道波形图不对,也最好指出。因为别人不知道你模块是干嘛的,从波形图很难短时间内看清楚哪里有问题。

2. 最好简单分析你自己的代码,并写出分析思路,你分析到哪里之后没办法再继续下去了,因为这样不用贴大段代码,只需要贴一部分,有助于别人帮你分析,这个如果你是在对verilog不了解倒也可以不用或者少分析。

3. 贴大段代码不是一个好方法,可是是在没办法的话,起码可以做到把代码编辑的漂亮一点,这样别人好看。一行定义一个变量,两个空格的缩进也是很必要的。

实际上,我花了两分钟看这个代码,一眼没看出来什么问题。

我知道啦 下次争取改进 这个我用function仿真就没问题了