异步FIFO采用格雷码

小伙网上到处有解释,你搜下,主动学习~

是格雷码每次只变化1比特,所以在异步过渡时更不容易出错。

话是这样说,格雷码是二进制转换来的,二进制会有毛刺,那转换来的格雷码也不一定正确啊!我这样理解对吗?

我一直在看,但是没有一个权威的说法,有的设计二进制转格雷码用的时序逻辑,有的用的组合逻辑,都可以吗?你能推荐一个好点的文档吗?

地址原二进展转换成gray码,再做同步,配合正确的SDC,可以保证同步后的地址不会出现异常值;比如原地址跳变为0、1、2、3、4、5,那么先gray再同步后,看到的地址可能为0、2、4,但是不会出现非0~5的值;这样保证了另一侧的空满判断不会出错,当然空满判断是不及时的

原来如此,谢谢了

格雷码的特点是,相邻数字只改变一位。而异步fifo中,经常会将读指针同步到写,写指针同步到读,当信号跳变时容易出现亚稳态。十进制相邻数字的变化很大,如从7(0111)变到8(1000)四位都需要变化,这就使得出错的概率大大增加

你好,我有点疑问,采用二进制码由于各bit延时不同的确会产生毛刺,可能采到错误的值,但是这个值应该不会产生读写数据错误。原因如下: 假设将clk2(读)的计数器同步到clk1(写)时钟域,且都假设为上升沿采样,那么产生毛刺时应该是clk2和clk1的上升沿很接近使clk2的数据传递到clk1不满足建立保持时间;但是在clk1下一次采样的时候,clk2和clk1的上升沿很可能就错开了(因为是异步时钟,不太可能接连两个上升沿都采到错误的值),这个时候采样得到的值为正确的值。(请继续往下看)

这里我们考虑FIFO满的产生。如果初始状态处于满状态,经过第一次错误采样后,clk1错误的判断为非满状态,于是写入了一个数据,但是此时已经读出一个数据(就在错误采样上升沿时读出的),FIFO中产生了一个空的位置,所以写数据不会覆盖有效数据,即使第一次采样错误,如果下一次采样正确的情况下,写数据就不会再向里写数据了,即数据安全。

不知道分析有问题没?望指正!

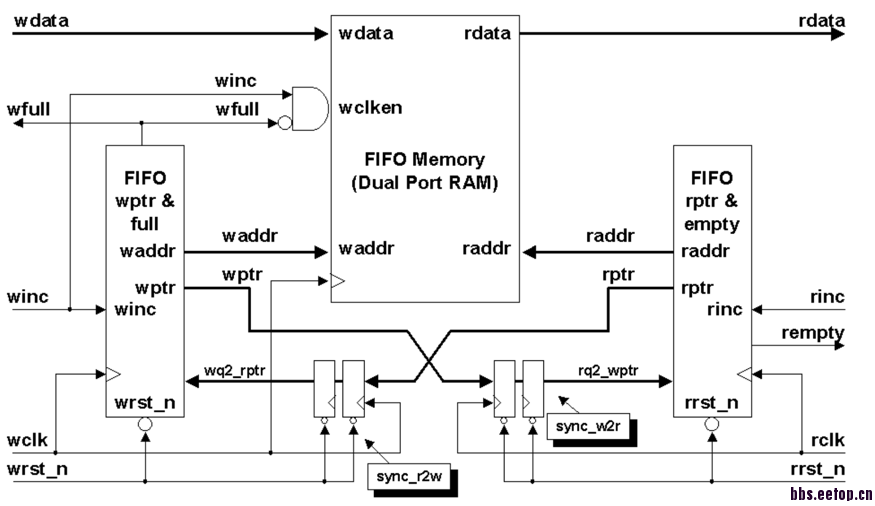

在读写模块都分别有一个格雷码转换二进制和二进制转换格雷码的模块,对于fifo memory,读写指针可以用二进制指针。但是在同步时,即读指针同步到写时钟域和写指针同步到读时钟域,用的是格雷码,可以加两个flop,来使读写互相同步。具体看下图block diagram。

你举得这个fifo满时的例子,实际是当读模块监测到fifo满时,就不会再写入任何数据了,写使能会置0。虽然此时会有读操作,从fifo memory读取走了数据,使得fifo实际上不“满”了,但此时写模块仍不会写入数据,原因你也肯定明白––就是因为读指针在同步到写时钟域时经过的那两个同步fifo会产生延迟,使得写短“反应慢了”。这样其实是损失了一定的fifo depth,损失了一部分性能,但是保证了数据的稳定。

推荐你拜读下Cliff Clummings的那两篇异步fifo的paper,简直醍醐灌顶。

懂了,讲的很详细,3q