求教一个timing约束问题

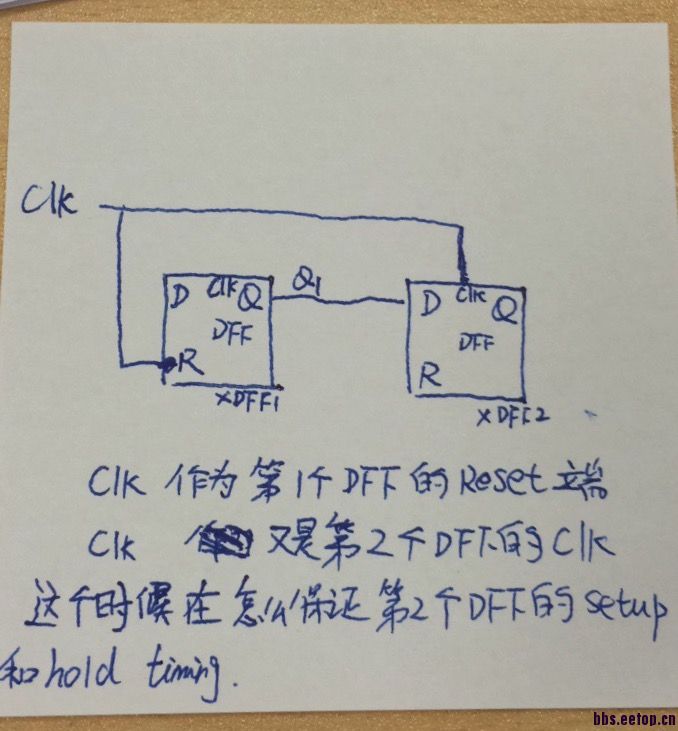

大家好,如上图中所述:

clk作为第1个dff的reset端,同时又是第2个dff的clk,

2个dff的reset 都是go high reset,第1个dff有自己的输入d和clock(图中没有画出来,因为此时q1是由reset决定的),2个dff的clock是不一样的,不同的时钟域。

这种情况如何让design complier保证第2个dff的setup和hold timing?目前simulation report好像不会check 这条path

需要写什么特殊的约束条件?

谢谢!

偏移约束?

感谢回复!但是不明白您说的意思 ,能否详细一点,我是菜鸟,谢谢!

百度一下,讲的应该详细 我也不熟

第一个寄存器没有时钟驱动,

没有launch clock,工具怎么进行建立保持时间的分析.

不好意思问一下小编,这个设计的目的是什么呢?

输出应该是常0啊

真神奇的电路,如果第一个DFF其实是Latch倒是有!

第一级DFF没有时钟驱动,没有launch clock,不存在同一时钟域下的常规的时序路径。

但在时钟切换下,第一级DFF响应异步复位,会将其输出端Q置到复位值,传递到DFF2的D端。

此时为了满足第二级DFF的建立时间,必须约束DFF1/R到DFF2/D的数据路径长度。

DFF1的R为低电平有效,即CLK下降沿触发复位输出传递到DDF2/D必须在T(半周期-DFF2的建立时间)内完成。用set_max_dely T/2-setup(DFF2) -to DFF2/D,由于是下降沿开始,保持时间天然存在半周期的余量,不需要做特殊设置。

感谢回复!你好,2个dff是一样的,图上面没有画清楚,都是go high reset,第1个dff也有它的输入和自己的clock(图中没有画出来),2个dff的clock是不一样的。由于go high reset,所以第2个dff 没有半个cycle的时间来保证timing。目前情况是timing report 中显示 sta分析工具没有check 这种path,所以比较奇怪,不知道怎么设置才能让工具check这种path,还是说工具本来就不能check 这种case。

感谢回复!你好,不好意思,图没有画清楚,第1个dff也有它的输入d和自己的clock),2个dff的clock是不一样的。

电路是代码综合出来的,但是检查的时候发现这一条path没check。如果是自己设计电路,估计不会用这种设计。

你使用的是什么器件啊?

Altera的话应该能分析到的,你检查一下时序约束里面, false path 的设置 和clock group的设置。

你好,器件用的是自己公司的工艺库,使用dc综合的。

真神奇的电路,如果第一个DFF其实是Latch倒是有!