Altera Stratix V LVDS clock tree问题

时间:10-02

整理:3721RD

点击:

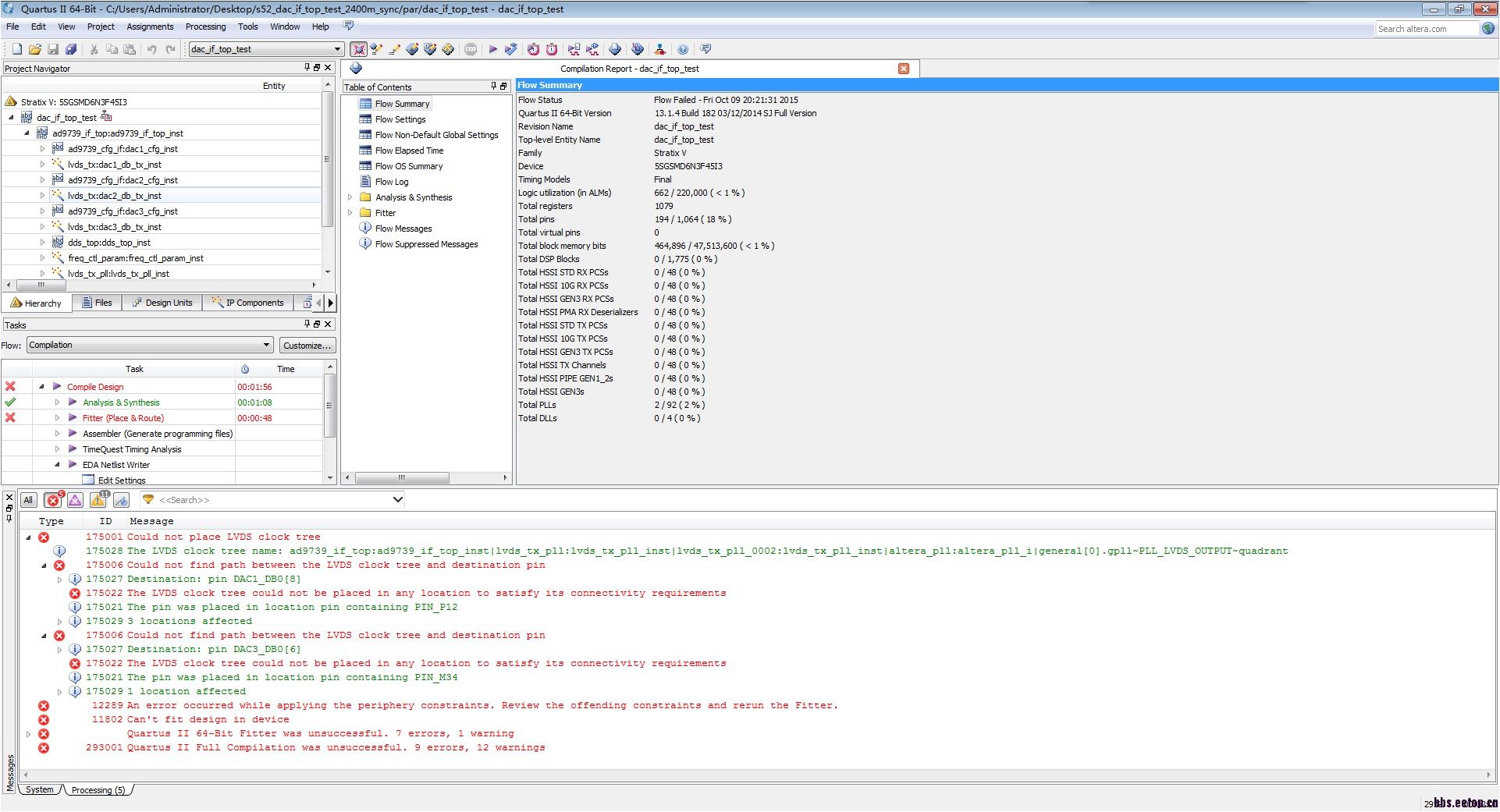

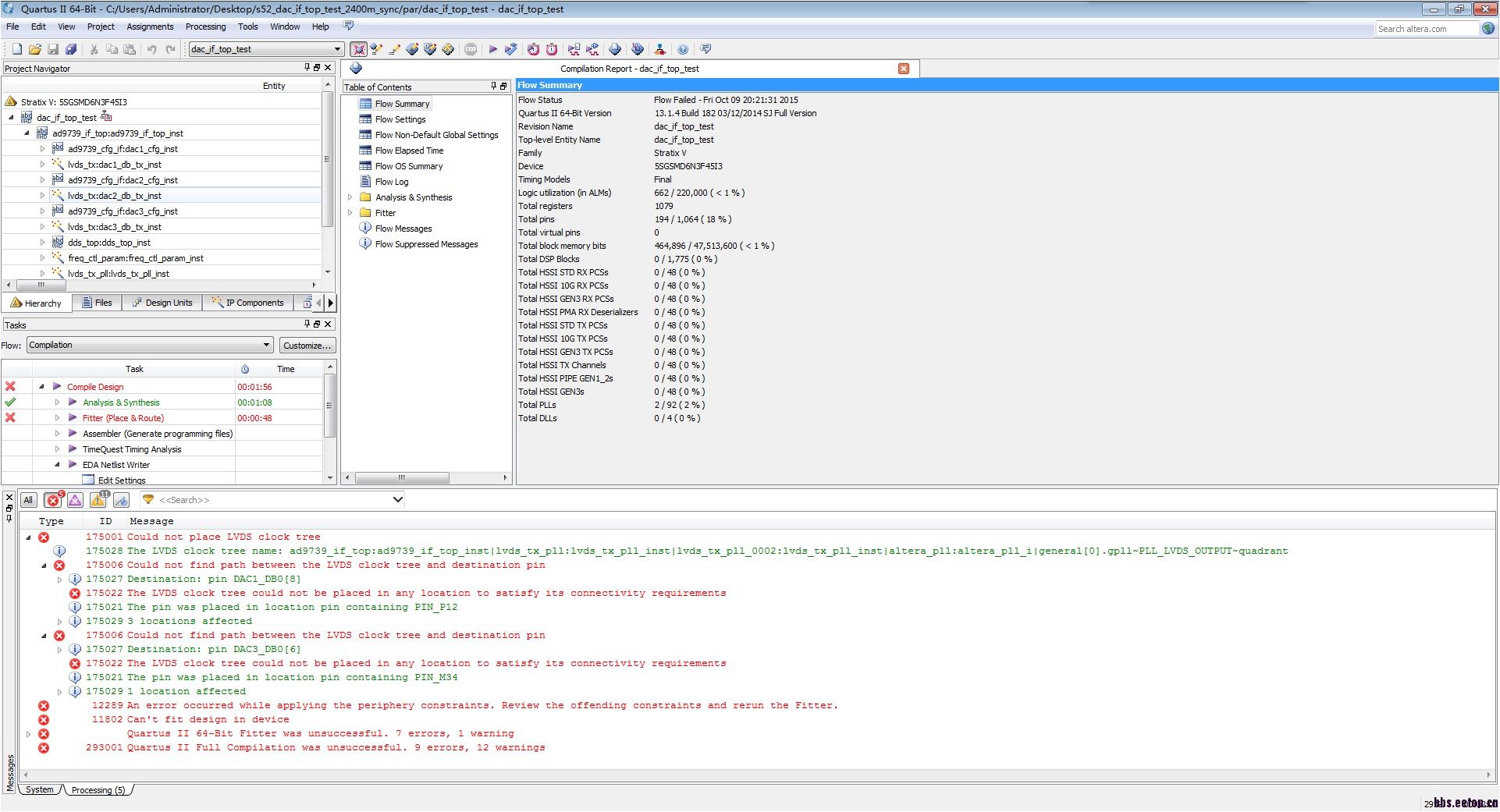

本人有个3片AD9739同步工程,FPGA为Altera的S5,AD9739采样率为2.4GHz,FPGA给AD9739的出数据和随路时钟采用altlvds_tx的外部锁相环方式。工程在fitter步过不去,报错如下图所示,求助大虾指点。

9739是DAC芯片?

嗯。